# MP1763B Pulse Pattern Generator Operation Manual

#### **Fourteenth Edition**

Read this manual before using the equipment.

Keep this manual with the equipment.

Digital. com Division

Measurement Solutions

ANRITSU CORPORATION

Document No.: M-W1023AE-14.0

# Safety Symbols

To prevent the risk of personal injury or loss related to equipment malfunction, Anritsu Corporation uses the following safety symbols to indicate safety-related information. Insure that you clearly understand the meanings of the symbols BEFORE using the equipment.

Some or all of the following symbols may not be used on all Anritsu equipment. In addition, there may be other labels attached to products which are not shown in the diagrams in this manual.

#### Safety Symbols Used in Manual

DANGER **A**

This indicates a very dangerous procedure that could result in serious injury or death if not performed properly.

**WARNING (**

This indicates a hazardous procedure that could result in serious injury or death if not performed properly.

**CAUTION (A)**

This indicates a hazardous procedure or danger that could result in light-to-severe injury, or loss related to equipment malfunction, if proper precautions are not taken.

#### Safety Symbols Used on Equipment and/or in Manual

The following safety symbols are used inside or on the equipment near operation locations, and/or in manual to provide information about safety items and operation precautions. Insure that you clearly understand the meanings of the symbols and take the necessary precautions BEFORE using the equipment.

This indicates a prohibited operation. The prohibited operation is indicated symbolically in or near the barred circle.

This indicates an obligatory safety precaution. The obligatory operation is indicated symbolically in or near the circle.

This indicates warning or caution. The contents are indicated symbolically in or near the triangle.

This indicates a note. The contents are described in the box.

These indicate that the marked part should be recycled.

MP1763B

Pulse Pattern Generator

Operation Manual

30 August 1995 (First Edition)

12 October 2000 (Fourteenth Edition)

Copyright © 1995-2000, ANRITSU CORPORATION.

All rights reserved. No part of this manual may be reproduced without the prior written permission of the publisher.

The contents of this manual may be changed without prior notice.

#### For Safety

#### **WARNING**

ALWAYS refer to the operation manual when working near locations at which the alert mark shown on the left is attached. If the operation, etc., is performed without heeding the advice in the operation manual, there is a risk of personal injury. In addition, the equipment performance may be reduced.

Moreover, this alert mark is sometimes used with other marks

and descriptions indicating other dangers.

2. When supplying power to this equipment, connect the accessory 3-pin power cord to a 3-pin grounded power outlet. If a grounded 3-pin outlet is not available, before supplying power to the equipment, use a conversion adapter and ground the green wire, or connect the frame ground on the rear panel of the equipment to ground. If power is supplied without grounding the equipment, there is a risk of receiving a severe or fatal electric shock.

Repair

WARNING 🛆

3. This equipment cannot be repaired by the user. DO NOT attempt to open the cabinet or to disassemble internal parts. Only Anritsu-trained service personnel or staff from your sales representative with a knowledge of electrical fire and shock hazards should service this equipment. There are high-voltage parts in this equipment presenting a risk of severe injury or fatal electric shock to untrained personnel. In addition, there is a risk of damage to precision parts.

Falling Over

This equipment should be used in the correct position. If the cabinet is turned on its side, etc., it will be unstable and may be damaged if it falls over as a result of receiving a slight mechanical shock.

## For Safety

#### **CAUTION**

Changing Fuse

CAUTION A

Before changing the fuses, ALWAYS remove the power cord from the poweroutlet and replace the blown fuses. ALWAYS use new fuses of the type and rating specified on the fuse marking on the rear panel of the cabinet.

T\_\_\_A indicates a time-lag fuse.

\_\_\_A or F\_\_\_ A indicate a normal fusing type fuse.

There is risk of receiving a fatal electric shock if the fuses are replaced with the power cord connected.

- 2. Keep the power supply and cooling fan free of dust.

- Clean the power inlet regularly. If dust accumulates around the power pins, there is a risk of fire.

- Keep the cooling fan clean so that the ventilation holes are not obstructed. If the ventilation is obstructed, the cabinet may overheat and catch fire.

Cleaning

3. Use two or more people to lift and move this equipment, or use a trolley. There is a risk of back injury, if this equipment is lifted by one person.

## **Equipment Certificate**

Anritsu Corporation certifies that this equipment was tested before shipment using calibrated measuring instruments with direct traceability to public testing organizations recognized by national research laboratories including the Electrotechnical Laboratory, the National Research Laboratory of Metrology and the Communications Research Laboratory, and was found to meet the published specifications.

## **Anritsu Warranty**

Anritsu Corporation will repair this equipment free-of-charge if a malfunction occurs within 1 year after shipment due to a manufacturing fault, provided that this warranty is rendered void under any or all of the following conditions.

- The fault is outside the scope of the warranty conditions described in the operation manual.

- The fault is due to misoperation, misuse, or unauthorized modification or repair of the equipment by the customer.

- The fault is due to severe usage clearly exceeding normal usage.

- The fault is due to improper or insufficient maintenance by the customer.

- The fault is due to natural disaster including fire, flooding and earthquake, etc.

- The fault is due to use of non-specified peripheral equipment, peripheral parts, consumables, etc.

- The fault is due to use of a non-specified power supply or in a non-specified installation location.

In addition, this warranty is valid only for the original equipment purchaser. It is not transferable if the equipment is resold.

Anritsu Corporation will not accept liability for equipment faults due to unforeseen and unusual circumstances, nor for faults due to mishandling by the customer.

## **Anritsu Corporation Contact**

If this equipment develops a fault, contact Anritsu Corporation or its representatives at the address in this manual.

#### Storage medium

This instrument uses floppy disks for storing data and programs.

Incorrect use of the floppy disks or errors can cause the data stored on the medium to be erased.

Back up the floppy disk as a precaution.

Anritsu will not compensate for loss of the stored data.

Note the following points when using this instrument. Especially, do not remove the floppy disk from the drive during disk access. For details, see the main text of this manual.

- Satisfy the specified environmental conditions. Do not use this instrument in ;places subject to dirt.

- Clean head of floppy disk drive with 3.5 inch head cleaning disk set regularly.

- Keep floppy disks away from magnetized products. Do not bend the floppy disk.

#### **Disposing of the product**

The MP1763B uses chemical compound semiconductor including arsenic and timer including manganese dioxide Lithium Battery and mercury.

At the end of it's life, the MP1763B should be recycled or disposed properly.

### **CE Marking**

Anritsu affix the CE Conformity Marking on the following product (s) in accordance with the Council Directive 93/68/EEC to indicate that they conform with the EMC directive of the European Union (EU).

#### **CE Conformity Marking**

#### 1. Product Name/Model Name

Product Name: Pulse pattern Generator

Model Name: MP1763B

#### 2. Applied Directive

EMC: Council Directive 89/336/EEC Safety: Council Directive 73/23/EEC

#### 3. Applied Standards

EMC:

Electromagnetic radiation:

EN55011 (ISM, Group 1, Class A equipment)

Immunity:

EN50082-1

|                               | Performance Criteria* |

|-------------------------------|-----------------------|

| IEC801-2 (ESD) 4 kVCD, 8 kVAD | В                     |

| IEC801-3 (Rad.) 3 V/m         | A                     |

| IEC801-4 (EFT) 1 kV           | В                     |

|                               |                       |

<sup>\*:</sup> Performance Criteria

A: No performance degradation or function loss

B: Self-recovered temporary degradation of performance or temporary loss of function

Harmonic current emissions:

EN61000-3-2 (Class A equipment)

Safety: EN61010-1 (Installation Category II, Pollution Degree 2)

(Blank)

#### **Title of Contents**

| For Safety |         |                                                        |  |  |  |

|------------|---------|--------------------------------------------------------|--|--|--|

| SECTION 1  | GENERAL |                                                        |  |  |  |

|            | 1.1     | Features                                               |  |  |  |

|            | 1.2     | Specifications                                         |  |  |  |

|            | 1.3     | Options                                                |  |  |  |

|            | 1.4     | Composition                                            |  |  |  |

| SECTION 2  | PRE     | CPARATIONS                                             |  |  |  |

|            | 2.1     | Environmental Conditions of Installation Site          |  |  |  |

|            | 2.2     | Safety Measures                                        |  |  |  |

|            | 2.3     | Power Supply Voltage                                   |  |  |  |

|            | 2.4     | Internal Battery Life                                  |  |  |  |

|            | 2.5     | Damage Prevention Measures                             |  |  |  |

| SECTION 3  | DES     | SCRIPTION OF PANELS AND CONNECTORS                     |  |  |  |

|            | 3.1     | FRONT PANEL                                            |  |  |  |

|            | 3.2     | REAR PANEL                                             |  |  |  |

| SECTION 4  | OPE     | ERATING INSTRUCTIONS 4                                 |  |  |  |

|            | 4.1     | Internal Clock Generator Frequency Setting (OPTION 01) |  |  |  |

|            | 4.2     | Generation Pattern Setting                             |  |  |  |

|            |         | 4.2.1 Logic modification                               |  |  |  |

|            |         | 4.2.2 Alternate pattern setting                        |  |  |  |

|            |         | 4.2.3 DATA pattern setting                             |  |  |  |

|            |         | 4.2.4 ZERO SUBSTITUTION                                |  |  |  |

|            |         | 4.2.5 Pseudo random pattern setting                    |  |  |  |

|            |         | 4.2.6 ERROR addition                                   |  |  |  |

|            |         | 4.2.7 Tracking                                         |  |  |  |

|            |         | 4.2.8 Pattern SYNC position                            |  |  |  |

|            | 4.3     | Output Interface 4                                     |  |  |  |

|            |         | 4.3.1 DUMMY terminal voltage switching                 |  |  |  |

|            |         | 4.3.2 Amplitude, offset, and delay setting             |  |  |  |

|            |         | 4.3.3 Duty adjustment                                  |  |  |  |

|            |         | 4.3.4 Cross point adjustment                           |  |  |  |

|            |         | 4.3.5 Offset voltage setting range                     |  |  |  |

|            |         |                                                        |  |  |  |

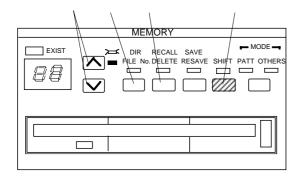

|           | 4.4 MEMORY (Floppy Disk)                      |

|-----------|-----------------------------------------------|

|           | 4.4.1 File save                               |

|           | 4.4.2 File recall                             |

|           | 4.4.3 Disk formatting                         |

|           | 4.4.4 File deletion                           |

|           | 4.4.5 Error messages4                         |

|           | 4.4.6 Floppy disk                             |

|           | 4.4.7 Floppy disk precautions                 |

|           | 4.5 Parameters initialization                 |

|           | 4.6 Functions of the FUNCTION Switch          |

| SECTION 5 | PRINCIPLES OF OPERATION                       |

|           | 5.1 Pseudorandom Pattern (PRBS Pattern)       |

|           | 5.2 Pattern Synchronized Output Period        |

|           | 5.2.1 Pseudorandom pattern                    |

|           | 5.2.2 Programmable pattern                    |

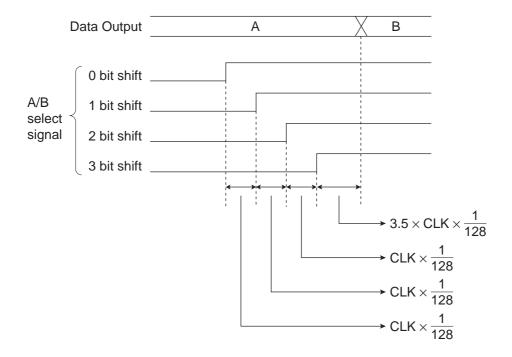

|           | 5.3 Bit shift for Alternate A/B select timing |

| SECTION 6 | PERFORMANCE TEST                              |

|           | 6.1 Test Equipment                            |

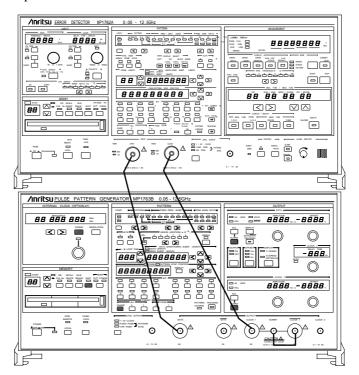

|           | 6.2 Error Measurement                         |

|           | 6.3 Test Method                               |

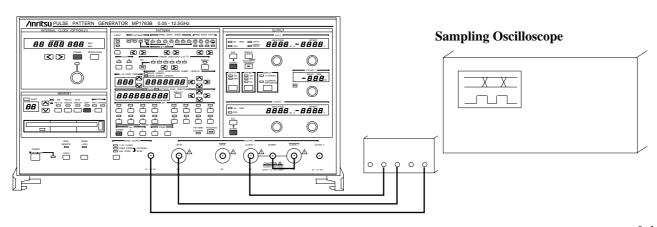

|           | 6.4 Waveform Check                            |

|           | 6.5 Check Items                               |

| SECTION 7 | CALIBRATION                                   |

| SECTION 8 | MAINTENANCE                                   |

|           | 8.1 Daily Maintenance                         |

|           | 8.2 Preparation for Shipment                  |

| SECTION 9 | TROUBLESHOOTING AND REPAIR                    |

|           | 9.1 Before Considering Trouble                |

|           | 0.2 Fusa Panlacament                          |

# SECTION 1 GENERAL

#### 1.1 Features

The MP1763B Pulse Pattern Generator has two data output channels (DATA and DATA) and three clock output channels (CLOCK1, CLOCK1, CLOCK2). The MP1763B is used with the MP1764A Error Detector to test high-speed digital communication systems and high-speed semiconductors. It operates over the 50 MHz to 12.5 GHz frequency range and generates four pulse patterns: alternate, programmable, zero substitution, and pseudorandom. Programmable DATA pattern can generate data up to 8 M bits and send six STM-64(OC192) frames.

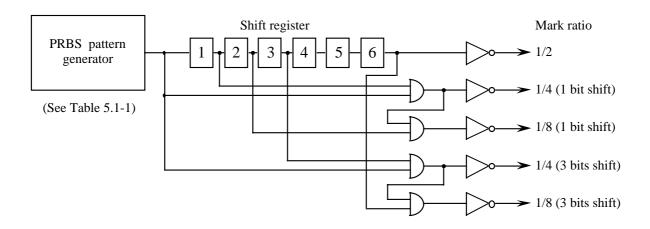

There are also seven  $2^N$ -1 (N=7, 9, 11, 15, 20, 23, 31) pseudorandom patterns. The pseudorandom pattern mark ratio can be selected from among 0/8, 1/8, 1/4, 1/2,  $\overline{1/2}$ , 3/4,  $\overline{7/8}$ , and 8/8. Both 50 $\Omega$  GND and ECL outputs are supported. The offset and level can be varied. The clock (CLOCK1, CLOCK1) delay can also be adjusted by  $\pm$  500ps in 1ps steps.

#### 1.2 Specifications

| Operation               | e Internal Clock (OPTION 01)  External Clock |                                                          | 0.05 to 12.5 GHz                                                                                                                                                                                                                                                               |

|-------------------------|----------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| frequency range         |                                              |                                                          | 0.05 to 12.5 GHz                                                                                                                                                                                                                                                               |

| Pattern PRBS generation |                                              | Pattern length                                           | 2 <sup>N</sup> -1 (N=7,9,11,15,20,23,31)                                                                                                                                                                                                                                       |

|                         |                                              | Mark ratio                                               | $\frac{1/2,1/4,1/8,0/8}{(1/2,3/4,7/8,8/8 \text{ also possible by logic inversion)}$                                                                                                                                                                                            |

|                         |                                              | Number of "AND<br>bit" shifts when setting<br>mark ratio | 1 bit or 3 bits<br>(Selectable using rear panel DIP switch)                                                                                                                                                                                                                    |

|                         | Zero subs                                    | titution                                                 | Continuous 0 pattern can be inserted up to pattern length -1. Patterns: 2 <sup>7</sup> , 2 <sup>9</sup> , 2 <sup>11</sup> , 2 <sup>15</sup>                                                                                                                                    |

|                         | DATA                                         | DATA length                                              | 2 to 8388608 bits  2 to 65536 : Step 1 bit 65536 to 131072 : Step 2 bits 131072 to 262144 : Step 4 bits 262144 to 524288 : Step 8 bits 524288 to 1048576 : Step 16 bits 1048576 to 2097152 : Step 32 bits 2097152 to 4194304 : Step 64 bits 4194304 to 8388608 : Step 128 bits |

|                         |                                              | Edit function                                            | All 0 / All 1 / Page 0 / Page 1                                                                                                                                                                                                                                                |

| Alternate pattern       |                                              |                                                          | Number of patterns A and B to be output can be specified.  Patterns A and B must be the same length.                                                                                                                                                                           |

|                         |                                              | Output control                                           | Internal/external switchable                                                                                                                                                                                                                                                   |

|                         |                                              | A/B switching                                            | A/B each 1 to 127 times/step 1                                                                                                                                                                                                                                                 |

|                         |                                              | DATA length                                              | 128 to 4194304 bits/step 128 bits                                                                                                                                                                                                                                              |

|                         |                                              | Edit function                                            | All 0 / All 1 / page 0 / page 1                                                                                                                                                                                                                                                |

|                         | Logic Positive / Negative swinnersion [PRBS] |                                                          | ching possible                                                                                                                                                                                                                                                                 |

|                         |                                              | H——  L  [PRGM]                                           | Positive Negative  "1"  H "1"  Positive Negative  Negative "0"                                                                                                                                                                                                                 |

|                         |                                              | L—                                                       | L "1"                                                                                                                                                                                                                                                                          |

| Pattern      | Error         | Internal                   | Error ratio        | $1 \times 10^{-n}$ or single $(n = 4, 5, 6, 7, 8, 9)$                                                                                                                                       |  |

|--------------|---------------|----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| generation   |               |                            | Insertion          | Insertion possible at any one of 32 channels                                                                                                                                                |  |

|              |               |                            | position           | (Rear panel swith)                                                                                                                                                                          |  |

|              |               | External                   | Eror injection     | Error insertion by rising edge of external signal input                                                                                                                                     |  |

|              |               |                            | Insertion position | Insertion possible at any one of 32 channels (Rear panel switch)                                                                                                                            |  |

|              |               |                            | DISABLE function   | Error insertion when external signal input level is "H"                                                                                                                                     |  |

|              |               |                            | Error ratio        | $1 \times 10^{-n}$ or single $(n = 4, 5, 6, 7, 8, 9)$                                                                                                                                       |  |

|              |               |                            | Insertion position | Insertion possible at any one of 32 channels (Rear panel switch)                                                                                                                            |  |

|              | Gating inpu   | ut                         | DATA is se         | t to "0" while external signal input level is "L".                                                                                                                                          |  |

| External     | Frequency     | range                      | 0.05 to 12.5       | 5 GHz                                                                                                                                                                                       |  |

| Clock Input  | Input level   | 1                          | 0.4 to 2.5 V       | <sup>7</sup> p-p                                                                                                                                                                            |  |

|              | Input wave    | form                       |                    | GHz : Square wave only                                                                                                                                                                      |  |

|              |               |                            | > 0.5 GHz:         | Sine wave or square wave (duty 50%)                                                                                                                                                         |  |

|              | Input impe    | dance                      | 50                 |                                                                                                                                                                                             |  |

|              |               | Connector                  |                    |                                                                                                                                                                                             |  |

| Clock output | outputs       |                            |                    | CLOCK1, CLOCK2 3 systems                                                                                                                                                                    |  |

|              | CLOCK1        | Delay rar                  | nge                | ± 500ps/1ps step                                                                                                                                                                            |  |

|              | / CLOCK1      | Amplitud                   | de                 | 0.25 to 2.0 Vp-p/Step 2 mV                                                                                                                                                                  |  |

|              |               |                            |                    | Setting error: ± 15% (1.5 to 2.0 Vp-p), ± 25% (0.5 to 1.5 Vp-p),<br>± 100 mV(0.25 to 0.5 Vp-p)                                                                                              |  |

|              |               | Rise/fall times (10%–90%)  |                    | -2.0 to 2.0 V (VOH ) /Step 1 mV<br>Setting error: ± 15% or ± 15% of Amplitude, and ± 100 mV,<br>whichever is larger                                                                         |  |

|              |               |                            |                    | 8 GHz 1.5 to 2 Vp-p 35ps or less<br>< 8 GHz 1.5 to 2 Vp-p 50ps or less<br>8 GHz 1.0 to 1.5 Vp-p 40ps or less<br>< 8 GHz 1.0 to 1.5 Vp-p 55ps or less<br>8 GHz 0.25 to 1.0 Vp-p 45ps or less |  |

|              |               |                            |                    | < 8 GHz 0.25 to 1.0 Vp-p 60ps or less                                                                                                                                                       |  |

|              |               | Waveform                   | m distortion       | 15% or less or 150 mV, whichever is larger                                                                                                                                                  |  |

|              |               | Duty ratio adjust function |                    | Duty ratio can be adjusted by semifixed variable resistor                                                                                                                                   |  |

|              |               | Load imp                   | edance             | 50 (with back termination)                                                                                                                                                                  |  |

|              |               | Terminati                  | ion                | 50 /GND, 50 /-2 V                                                                                                                                                                           |  |

|              |               | Connecto                   | r                  | APC-3.5                                                                                                                                                                                     |  |

|              | CLOCK2 Output |                            | vel                | VOH: 0 ± 200 mV<br>Amplitude: 1 Vp-p ± 35%                                                                                                                                                  |  |

|              |               | Load imp                   | edance             | 50 (without back termination)                                                                                                                                                               |  |

|              |               | Connecto                   | or                 | SMA                                                                                                                                                                                         |  |

|              | 1             |                            |                    | I                                                                                                                                                                                           |  |

| DATA output  | Output waveform       | NRZ                                                                                                                                                                                           |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Number of outputs     | DATA, DATA 2 systems independence                                                                                                                                                             |

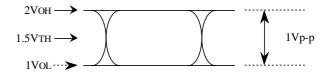

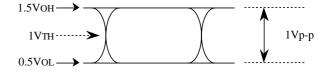

|              | Amplitude             | 0.25 to 2.0 Vp-p/Step 2 mV<br>Setting error: ±15% or ±100 mV, whichever is larger                                                                                                             |

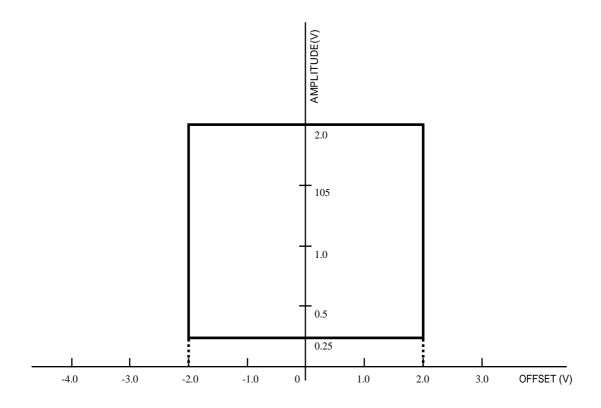

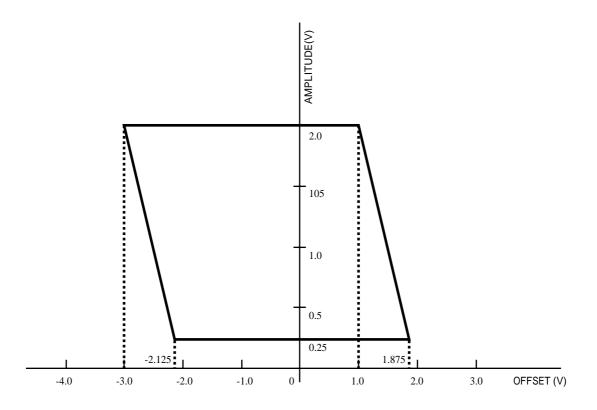

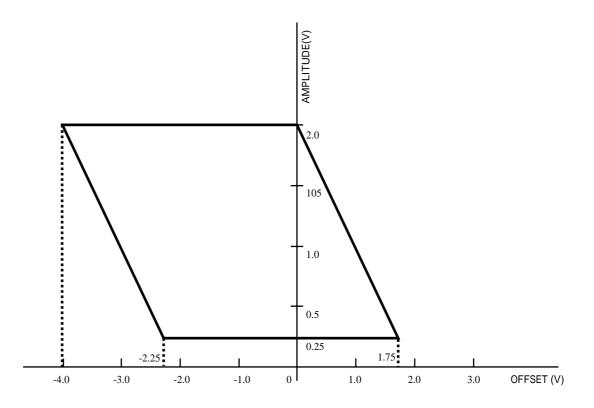

|              | Offset voltage        | -2.0 to 2.0 V (V <sub>OH</sub> ) /Step 1 mV<br>Setting error: ±15% or ±15% of Amplitude, and ±100 mV,<br>whichever is larger                                                                  |

|              | DATA/DATA<br>Tracking | Amplitude and offset of DATA and DATA can be set to the same value.                                                                                                                           |

|              | Rise / fall time      | 5 GHz, amplitude 1 to 2 Vp-p 35ps or less (10-90%) 5 GHz, amplitude 0.5 to 1 Vp-p 40ps or less (10-90%) 5 GHz, amplitude 0.25 to 0.5 Vp-p 45ps or less (10-90%) < 5 GHz 45ps or less (10-90%) |

|              | Pattern jitter        | 20ps or less (p-p)                                                                                                                                                                            |

|              | Waveform distortion   | 7% or less, or 100 mV or less, whichever is larger.                                                                                                                                           |

|              | Termination           | 50 /GND, 50 /-2 V                                                                                                                                                                             |

|              | Load impedance        | 50 (with back termination)                                                                                                                                                                    |

|              | Connector             | APC-3.5                                                                                                                                                                                       |

| Output phase | DATA                  | X                                                                                                                                                                                             |

|              | DATA                  | <b>▼</b> t1                                                                                                                                                                                   |

|              | CLOCK1                | t2                                                                                                                                                                                            |

|              | CLOCK1                | 13                                                                                                                                                                                            |

|              | CLOCK2                | t4                                                                                                                                                                                            |

|              |                       | t1  30ps<br>  t2  30ps<br>  t3  30ps<br>  t4  30ps                                                                                                                                            |

|              | CLOCK1/CL             | OCK1 delay set to 0ps                                                                                                                                                                         |

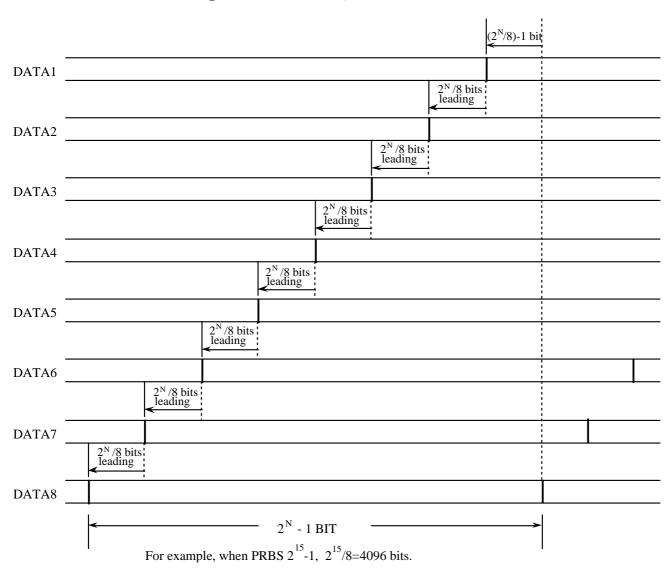

| 1/8 output                         | Number of output    | 8 data outputs, 1 clock output                                                            |  |  |  |

|------------------------------------|---------------------|-------------------------------------------------------------------------------------------|--|--|--|

|                                    | Data polarity       | Same as 1/1 DATA                                                                          |  |  |  |

|                                    | Output level        | ECL (H: -0.9 ± 0.25 V, L: -1.75 ± 0.25 V)                                                 |  |  |  |

|                                    | Rise / fall time    | 300 ps or less (20-80%)                                                                   |  |  |  |

|                                    | Pattern jitter      | 100 ps or less (p-p)                                                                      |  |  |  |

|                                    | Waveform distortion | 15% or less                                                                               |  |  |  |

|                                    | Skew                | 150 ps or less (relative to falling edge of 1/8 clock)                                    |  |  |  |

|                                    | Output bit rate     | 1/8 of fundamental frequency                                                              |  |  |  |

|                                    | Load impedance      | 50                                                                                        |  |  |  |

|                                    | Connector           | SMA                                                                                       |  |  |  |

| Sync. output                       |                     | Switching of 1/64 CLOCK, Fixed position pattern sync, and Variable position pattern sync. |  |  |  |

|                                    | Output level        | V <sub>OH</sub> : 0±200 mV Amplitude: 1 Vp-p±20%                                          |  |  |  |

|                                    | Load impedance      | 50                                                                                        |  |  |  |

|                                    | Connector           | SMA                                                                                       |  |  |  |

| Alternate pattern<br>A/B switching |                     | ALTN patterns A/B switching controlled by external signal                                 |  |  |  |

| input                              |                     | A B A                                                                                     |  |  |  |

|                                    |                     | 1                                                                                         |  |  |  |

|                                    | Minimum pulse width | Fundamental frequency × Data length                                                       |  |  |  |

|                                    | Input level         | ECL (H: $-0.9 \pm 0.2 \text{ V}$ , L: $-1.75 \pm 0.2 \text{ V}$ )                         |  |  |  |

|                                    | Input impedance     | 50                                                                                        |  |  |  |

|                                    | Connector           | SMA                                                                                       |  |  |  |

| Alternate pattern A/B switching    |                     | ALTN patterns A/B switching signal output                                                 |  |  |  |

| output                             |                     | A B A                                                                                     |  |  |  |

|                                    | Output level        | ECL (H: -0.9 ± 0.2 V, L: -1.75 ± 0.2 V)                                                   |  |  |  |

|                                    | Output impedance    | 50                                                                                        |  |  |  |

|                                    | Connector           | SMA                                                                                       |  |  |  |

| Error injection input              |                     | Error inserted at rising edge by external signal                                          |  |  |  |

| •                                  |                     |                                                                                           |  |  |  |

|                                    |                     | Error Error Error Error                                                                   |  |  |  |

|                                    | Minimum pulse width | Tundamental frequency x 32                                                                |  |  |  |

|                                    | Input level         | 0/-1 V                                                                                    |  |  |  |

|                                    | Input impedance     | 50                                                                                        |  |  |  |

|                                    | Connector           | SMA                                                                                       |  |  |  |

|                                    |                     | •                                                                                         |  |  |  |

| External Gating             | Input level Input impedance Connector                                            | Error ON/OFF controlled by external input signal  Error addition  Error rate can be selected over this range  0/-1 V  50  SMA  Output data control by external signal  Data  Data  Bottom  Data |  |

|-----------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| input                       |                                                                                  | "0" Data "0"                                                                                                                                                                                    |  |

|                             | Minimum pulse width                                                              | Tundamental frequency × 32                                                                                                                                                                      |  |

|                             | Input level                                                                      | 0/-1 V                                                                                                                                                                                          |  |

|                             | Input impedance                                                                  | 50                                                                                                                                                                                              |  |

|                             | Connector                                                                        | SMA                                                                                                                                                                                             |  |

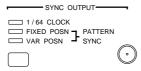

| Parameter                   | Medium                                                                           | 3.5 inch FD, 2HD, 2DD by 3 mode support                                                                                                                                                         |  |

| memory                      | Format                                                                           | MS-DOS format (IBM-PC/NEC-PC selectable by rear panel DIP switch)                                                                                                                               |  |

|                             | Stored data                                                                      | Programmable pattern/others                                                                                                                                                                     |  |

|                             | Mode switching                                                                   | Format, save, recall, resave, delete, search                                                                                                                                                    |  |

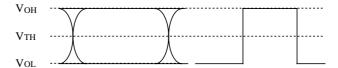

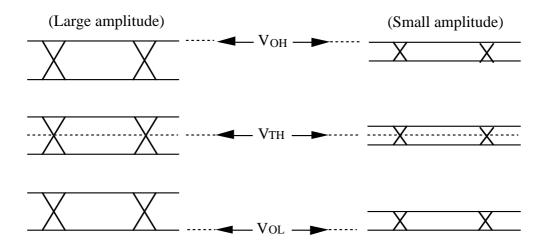

| Display                     | Display switching V <sub>OH</sub> , V <sub>TH</sub> , V <sub>OL</sub> switchable |                                                                                                                                                                                                 |  |

|                             | Panel lock Disables all keys other than power switch.                            |                                                                                                                                                                                                 |  |

| External control            | GPIB interface for one system                                                    |                                                                                                                                                                                                 |  |

| GPIB                        | GPIB connector for external control                                              |                                                                                                                                                                                                 |  |

| Initialization              | Inirialized by Local + Power on                                                  |                                                                                                                                                                                                 |  |

| Operating temperature range | 0 to 50                                                                          |                                                                                                                                                                                                 |  |

| Insulation resistance       | 2M or more at 500 V                                                              |                                                                                                                                                                                                 |  |

| Dielectric<br>strength      | 1.5 kV, for 1 minute                                                             |                                                                                                                                                                                                 |  |

| Power requirement           | 100 V system: 85 to 2<br>Frequency 50/60 Hz ±<br>700 VA or less                  | ·                                                                                                                                                                                               |  |

| Dimensions<br>& weight      | 221.5±4H × 426±5W >                                                              | <b>&lt;</b> 451±5D, 33 kg or less                                                                                                                                                               |  |

| Option-01   | Name                | Internal synthesizer                                                                                            |  |  |  |

|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

|             | Frequency range     | 0.05 to 12.5 GHz                                                                                                |  |  |  |

|             | Output level        | 0.5 to 2.3 Vp-p                                                                                                 |  |  |  |

|             | Resolution          | 1 kHz/1 MHz (switchable)                                                                                        |  |  |  |

|             | Frequency accuracy  | 1ppm (* When synchronized with external signal, accuracy is determined by external signal.)                     |  |  |  |

|             | Reference signal    | 10 MHz (internal/external switchable)                                                                           |  |  |  |

|             | Signal purity       | SSB phase noise (10 kHz offset, bandwidth 1 Hz)                                                                 |  |  |  |

|             |                     | 0.05 Freq. < 2.0 GHz -90 dBc                                                                                    |  |  |  |

|             |                     | 2.0 Freq. < 4.0 GHz -85 dBc                                                                                     |  |  |  |

|             |                     | 4.0 Freq. < 8.0 GHz -80 dBc                                                                                     |  |  |  |

|             |                     | 8.0 Freq. <10.0 GHz -75 dBc                                                                                     |  |  |  |

|             |                     | 10.0 Freq. 12.5 GHz -70 dBc                                                                                     |  |  |  |

|             | Spurious radiation  | At clock output terminal Nonharmonic –70 dBc or less (off carrier 10 kHz or more) Power supply –40 dBc or less  |  |  |  |

|             | Load impedance      | 50                                                                                                              |  |  |  |

|             | Connector           | SMA                                                                                                             |  |  |  |

| Option-03 * | Name                | 1/4 SPEED OUTPUT                                                                                                |  |  |  |

|             | Number of output    | 4 data outputs, 1 clock output                                                                                  |  |  |  |

|             | Output bit rate     | 1/4 of fundamental frequency                                                                                    |  |  |  |

|             | Data polarity       | Same as 1/1 DATA                                                                                                |  |  |  |

|             | Termination         | 50 /GND, 50 /–2 V                                                                                               |  |  |  |

|             | Amplitude           | 0.5 to 2.0 Vp-p/Step 2 mV<br>Setting error: ±15% or ±100 mV, whichever is larger                                |  |  |  |

|             | Offset voltage      | -1.5 to +1.5 V (Voн)/Step 1 mV<br>Setting error: ±15% or ±15% of Amplitude, and ±100 mV,<br>whichever is larger |  |  |  |

|             | Rise/fall time      | 150ps or less (20-80%)                                                                                          |  |  |  |

|             | Pattern jitter      | 100ps or less (p-p)                                                                                             |  |  |  |

|             | Waveform distortion | 15% or less                                                                                                     |  |  |  |

|             | Skew                | The $1/4$ data cross point is within $\pm 100$ ps relative to the falling edge of the $1/4$ clock.              |  |  |  |

|             | Output impedance    | 50                                                                                                              |  |  |  |

|             | Connector           | SMA                                                                                                             |  |  |  |

<sup>\*</sup> When OPTION 03 is installed, there is no 1/8 output.

#### 1.3 Options

The following options are available:

OPTION 01 Internal synthesizer OPTION 03 1/4 SPEED OUTPUT

#### 1.4 Composition

The standard composition of the MP1763B Pulse Pattern Generator is shown in Table 1.4-1.

Table 1.4-1 MP1763B Standard Composition

| Item        | No.       | Name                            | Qty |                          |

|-------------|-----------|---------------------------------|-----|--------------------------|

| Main Unit   | MP1763B   | MP1763B Pulse Pattern Generator | 1   |                          |

| Accessory   | J0500A    | Semirigid cable (50 cm)         | 2   |                          |

|             | J0672E    | Semirigid cable (10 cm)         | 1   |                          |

|             | J0496     | Conversion connector            | 4   | APC ¥ 3.5J-APC ¥ 3.5J    |

|             | J0693     | SMA cable (1 m)                 | 1   |                          |

|             | J0491     | Shield power cord               | 1   | 13A (2.6 m)              |

|             | J0008     | GPIB cable (2 m)                | 1   | 408JE-102                |

|             | F0071     | Fuse                            | 2   | MF51NR8A                 |

|             | Z0168     | 3.5 inch floppy disk (2HD)      | 2   | Formatted *              |

|             | Z0306A    | Wrist strap                     | 1   |                          |

|             | M-W1023AE | Operation manual                | 1   |                          |

|             | M-W1024AE | GPIB Operation manual           | 1   |                          |

|             | Z0481     | 12.5G/3.2G BERTS APPLICATION    | 1   |                          |

|             |           | SOFTWARE DEMO                   |     |                          |

| Application | MB24B     | Caster                          |     | with 20A power cord/plug |

| parts       | B0163     | Portable carrying case          |     |                          |

|             | B0171     | Protective carrying case        |     |                          |

|             | B0044     | For mounting kit 1MW ¥ 5U       |     | 2 pcs/set                |

|             | Z0416     | 3.5 inch head cleaning disk     |     |                          |

<sup>\*</sup> The capacity of the formatted type is 1,440 kilobytes. The quasi PRBS2<sup>10</sup>–1 patterns (mark ratio 1/2, 1/4, 1/8) are saved on one floppy disk.

# SECTION 2 PREPARATIONS

#### 2.1 Environmental Conditions of Installation Site

Do not use and store the instrument in the following locations:

- where vibrations are severe.

- where it is damp or dusty.

- where there is exposure to direct sunlight.

- where there is exposure to active gases.

Long-term storage at high temperatures will shorten the life of the internal battery. Store the instrument below normal room temperature.

Operating temperature range 0 to 50 (However, 5 to 40 for floppy disks). Storage temperature range -40 to 70

#### 2.2 Safety Measures

- Use the attached power cord to connect the AC power supply. Ground the ground terminal of the power cord or the frame ground terminal on the rear panel of the instrument.

- When changing the fuse, always use a fuse of the same rating. (See the fuse replacement item.)

- If the instrument is operated at room temperature after being used or stored for a long time at low temperature, condensation may occur and cause short-circuiting. To prevent this, do not turn the power on until the instrument completely dry.

#### 2.3 Power Supply Voltage

The power supply voltage for this instrument is shown on the rear panel. Use a voltage within the rated voltage range. Excessive voltage may damage the circuits.

#### 2.4 Internal Battery Life

This instrument uses a lithium primary battery as the timer and memory back-up power supply. The life of this battery is 7 years or more when the instrument is stored at normal room temperature. However, since the battery life largely depends on the storage temperature, storage at high temperatures for long periods will shorten the period above. Replace the battery of which period is exceeded. The internal battery cannot be recharged.

#### **Section 2 PREPARATIONS**

#### 2.5 Damage Prevention Measures

- Do not apply an excessive voltage when inputting the signal to this instrument. The circuits may be destroyed.

- Terminate the output with  $50\Omega$ . Do not feed current to the output. The load must be a  $50\Omega$  pure resistor terminated at ground potential.

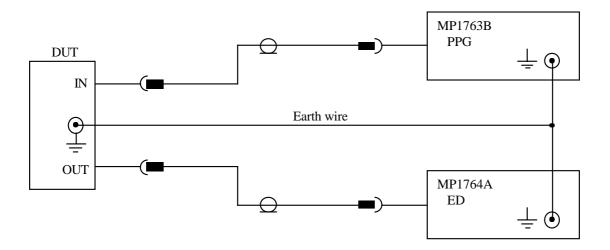

- Before connecting the input and output terminals, ground the other equipment (including test circuits) with a ground wire. (Static electric countermeasure)

- The outer and inner conductors of the coaxial cable may be charged as a capacitor. Therefore, discharge them with a piece of metal before using the cable.

- This instrument contains hybrid ICs and other important circuits and parts. These parts are extremely vulnerable to static electricity. Therefore, never remove the bottom cover.

- The hybrid ICs inside this instrument are hermetically sealed. Never break this seal. If the hybrid ICs are unsealed and the instrument deteriorates performance as specified, note that the maintenance may be refused.

- Ventilation holes are drilled into the bottom cover. Be careful not to block the ventilation.

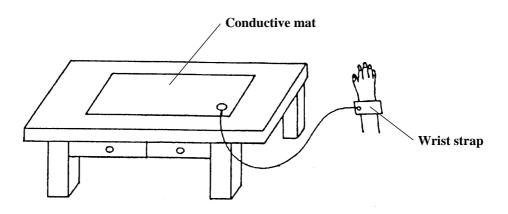

• To protect this instrument against electrostatic damage, place a conductive mat on the work bench, and wear a wrist strap. Connect the other end of the wrist strap to the conductive mat, or the GND terminal of this instrument.

# SECTION 3 DESCRIPTION OF PANELS AND CONNECTORS

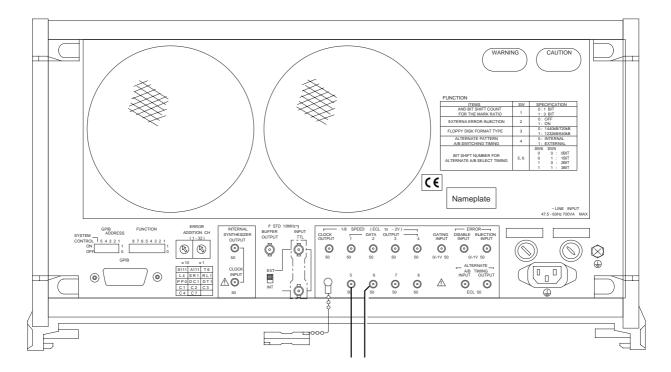

#### Section 3 DESCRIPTION OF PANELS AND CONNECTORS

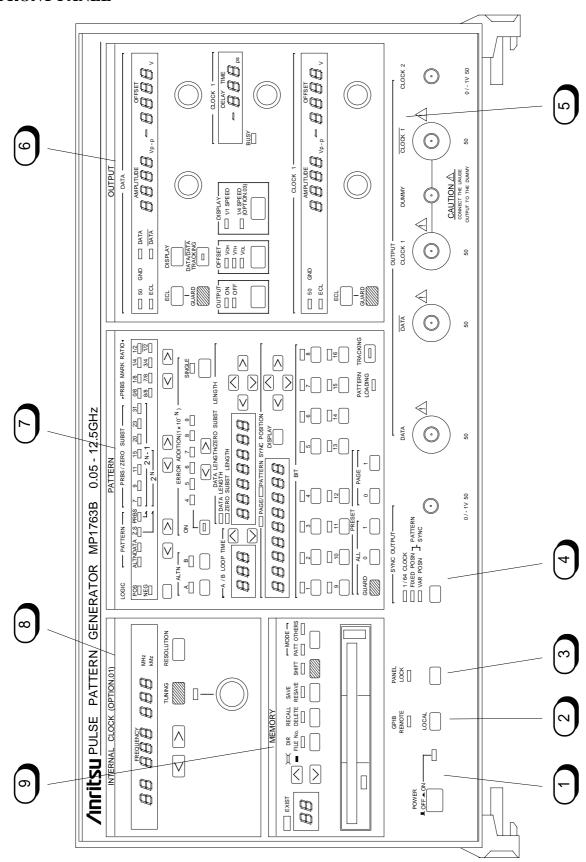

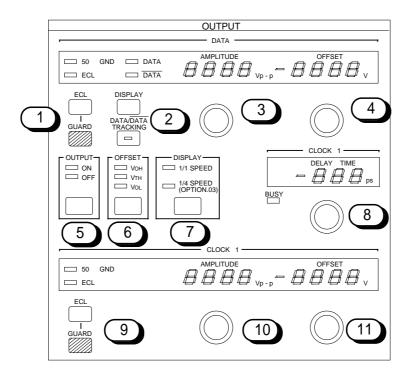

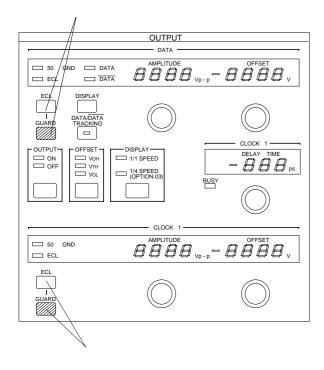

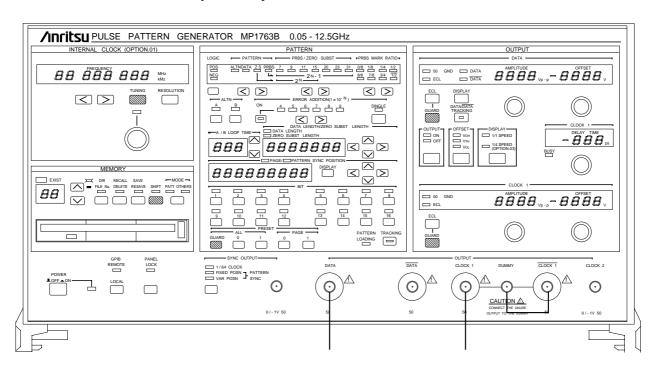

#### 3.1 FRONT PANEL

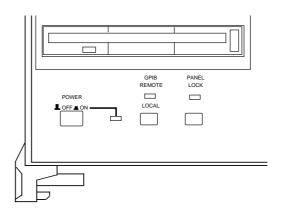

| Power switch        | When, the j                                                                                             | , the power is turned on and the LED goes on.<br>, the power is turned off.                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 LOCAL key         | Switches from the GPI                                                                                   | Switches from the GPIB REMOTE mode (LED lit) to the LOCAl (key operation possible) mode.                                                                                                                                                              |

|                     | In GPIB REMOTE mo                                                                                       | In GPIB REMOTE mode, all the keys other than the power switch and LOCAL key are ineffective.                                                                                                                                                          |

| 3 PANEL LOCK key    | Panel lock (LED lit) di                                                                                 | Panel lock (LED lit) disables all the keys other than the POWER switch and the PANEL LOCK key.                                                                                                                                                        |

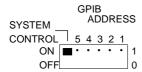

| SYNC OUTPUT keys    | Select the type of SYNC OUTPUT.  1/64 CLOCK: Outputs a CL FIXED POSITION: Outputs VARIABLE POSITION: Sh | the type of SYNC OUTPUT.  1/64 CLOCK: Outputs a CLOCK divided by 64.  FIXED POSITION: Outputs a synchronization pulse at a fixed position to the output pattem.  VARIABLE POSITION: Shifts the synchronization pulse output position in 16 bits unit. |

| 5 Output connectors | DATA, DATA CLOCK1, CLOCK1 CLOCK2 DUMMY                                                                  | Output.  Complementary CLOCK output.  Auxiliary clock output.  Connects the unused side of the complementary output.  Note: If the unused side of the complementary output is opened, the output waveform on the side used will be degraded.          |

Sets the output level, offset and termination conditions.

OUTPUT condition block

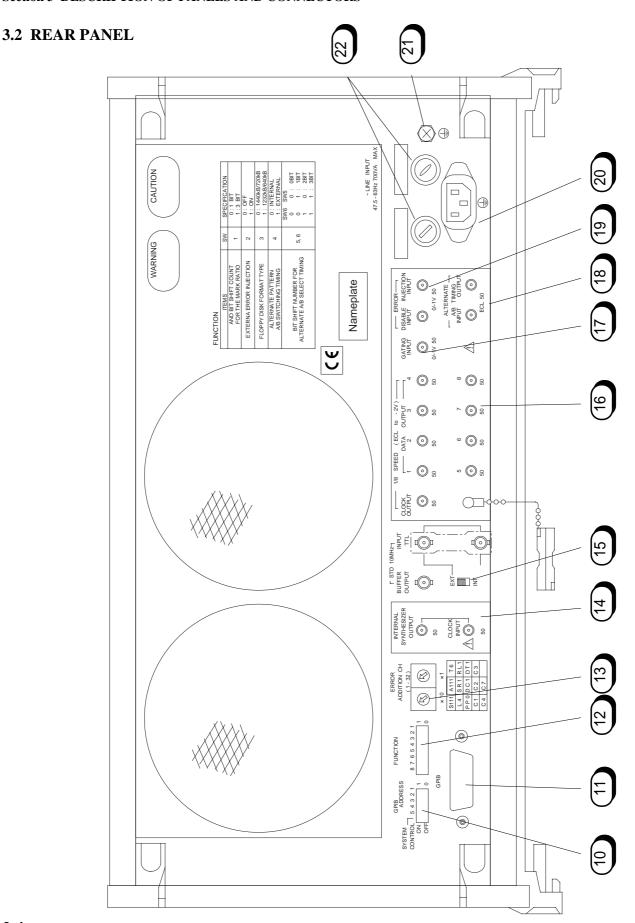

#### Section 3 DESCRIPTION OF PANELS AND CONNECTORS

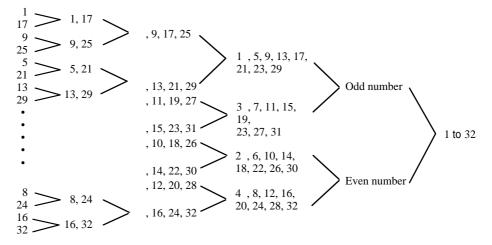

Sets the address when the instrument is remotely controlled by GPIB. It is usually set to

00000

SYSTEM CONTROL switch

When this switch is set to 'ON', this instrument control other one.

Connector for GPIB cable. (The cable is connected when the instrument is remotely controlled by GPIB.)

12

GPIB connector

7

It is possible to select functions noted rear panel. **FUNCTION Dip switch**

13

Selects which of the 32 channels an error is to be added. Error ADDITION CH

4

Internal CLOCK output connector when OPTION 01 installed INTERNAL SYNTHESIZER

Clock signal input connector. (When the internal synthesizer is used, this connector is connected to the INT. SYNTHE. CLOCK INPUT

OUTPUT connector.)

STD 10 MHz 15

When OPTION 01 (internal synthesizer) is used, synthesizes the other signals and the internal synthesizer.

10 MHz TTL level

16

1/8 DATA and 1/8 CLOCK output connector (ECL level) 1/8 SPEED output connector

Note: When OPTION 03 (1/4 SPEED OUTPUT) is installed, this connector becomes the 1/4 DATA, 1/4 CLOCK output

connector.

17

$0/-1 \text{ V} 50\Omega$ GATING signal input connector

18

ECL level  $50\Omega$ Alternate pattern A/B switching

Timing I-O connector

Error addition control connector

$50\Omega$

0/-1 V

19 20

Ground terminal Power inlet

Connected to the ground terminal of an instrument connected to this instrument.

Fuse holder

21

#### Section 3 DESCRIPTION OF PANELS AND CONNECTORS

# SECTION 4 OPERATING INSTRUCTIONS

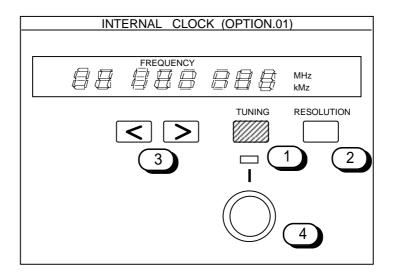

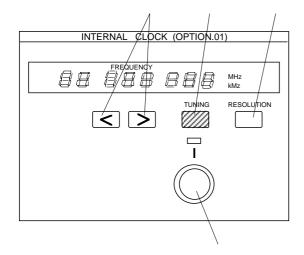

#### 4.1 Internal Clock Generator Frequency Setting (OPTION 01)

This section sets the frequency of the internal clock generator when the CLOCK generator (OPTION 01) is used.

1 TUNING ON/OFF

The frequency can be changed only when the TUNING LAMP is lit.

2 RESOLUTION

Used when setting the frequency down to the kHz order. Pressing this key again returns the setting to the MHz order.

3 <>

Select the digit to be changed. The figure of the digit to be changed blinks.

4

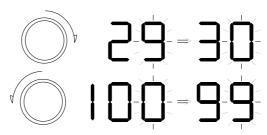

Used when changing the blinking digit.

The figure is carried over.

#### **Section 4 OPERATING INSTRUCTIONS**

Press the TUNING key. The TUNING lamp lights. (The frequency can be changed only when the TUNING lamp is lit.) At this time, the figure of the digit that can currently be changed blinks.

Press the RESOLUTION key and select whether the frequency is to be set in MHz or kHz.

When the frequency can be set down to kHz, an 8-digit number is displayed. (Five digits for MHz.)

Select the digit to be changed with the keys. The figure of the digit that can be changed blinks.

Change the frequency by turning the rotary encoder.

Note: The frequency may not be stable just after the power is turned on. Make a warm-up run for 10 minutes or longer before use.

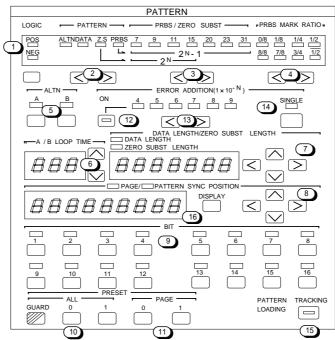

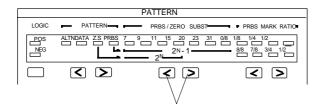

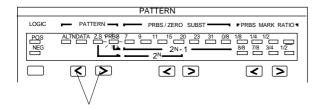

#### 4.2 Generation Pattern Setting

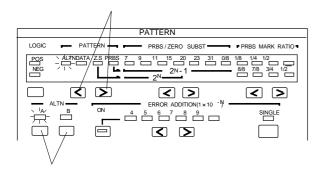

Error addition ON/OFF

Single error addition

Tracking ON/OFF

Error addition rate selection

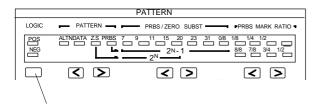

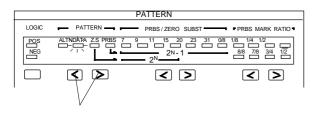

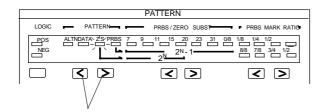

| 10                                   |                                                                                                                                                                                       |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC                                | Inverts the output pattern logic.                                                                                                                                                     |

| PATTERN                              | Selects the output pattern type.                                                                                                                                                      |

| PRBS/ZERO SUB                        | Selects the kind of pseudorandom pattern. (If ZERO SUB is selected, the $2^{\rm N}$ pattern is selected.)                                                                             |

| Mark ratio                           | Selects the output pattern (pseudorandom pattern) mark ratio.                                                                                                                         |

| Alternate                            | Selects alternate pattern A or B.                                                                                                                                                     |

| Number of alternate loops            | Sets the number of A or B pattern loops.                                                                                                                                              |

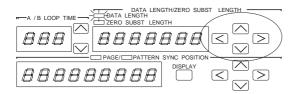

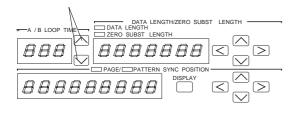

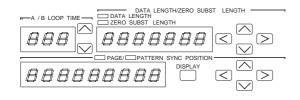

| DATA length/continuous 0 bits length | Sets the DATA length. For Z.S., sets the continuous 0 bit length.                                                                                                                     |

| PAGE/pattern sync position           | Sets the page selection (ALTN/DATA) and pattern synchronization position.                                                                                                             |

| Bit setting                          | Sets the output pattern for each 16 bits.                                                                                                                                             |

| Bit setting (special)                | Sets all DATA to 0 or 1.                                                                                                                                                              |

| Bit setting (special)                | Sets DATA to 0 or 1 in page units.                                                                                                                                                    |

|                                      | LOGIC  PATTERN  PRBS/ZERO SUB  Mark ratio  Alternate  Number of alternate loops  DATA length/continuous 0 bits length  PAGE/pattern sync position  Bit setting  Bit setting (special) |

Turns error addition on and off.

Selects the error addition rate.

key is pressed.

lowed by the other).

In the single error addition mode, one error is added each time this

When tracking is turned on, the settings of the transmitter and receiver are changed at the same time (the one set as the master is fol-

Display switching Selects page display or pattern sync position display.

4-3

#### **Section 4 OPERATING INSTRUCTIONS**

#### 4.2.1 Logic modification

The logic of the set pattern is changed in positive negative positive order each time the LOGIC key is pressed. (The set logic is indicated by lighting of a lamp.)

#### 4.2.2 Alternate pattern setting

Select ALTN with the keys

(DATA, Z.S, and PRBS are also selected with these keys.)

ALTN DATA Z.S. PRBS

ALTN DATA Z.S. PRBS

Pattern A and pattern B are selected with this key. Since pattern A is set first, set this key so that the A lamp lights. (It does not matter which pattern is set first.)

Set DATA LENGTH with the and keys. This value is common to both patterns A and B.

Select the digit to be set with the keys.

Set DATA LENGTH with the keys. Set value: 128 to 4,194,304 bits (128-bit steps)

Set the number of pattern A loops with the **\( \sum\_{\subset} \)** keys.

#### 4.2 Generation Pattern Setting

Change the BIT value with the button below the LED. When LOGIC is positive, lighting of the LED indicates high level.

Used the PRESET ALL or PAGE key when changing DATA collectively.

PAGE 0 or 1 All BITs of the displayed PAGE are set to 0 or

ALL 0 or 1 Pressing this key while holding down the GUARD key sets all BITs specified by DATA LENGTH to 0 or 1.

Next, set in pattern B (turn on the B LED) and set pattern B in the same way as pattern A.

However, do not change DATA LENGTH here because it is shared by A and B. If DATA LENGTH is changed here, DATA LENGTH of pattern A is also changed.

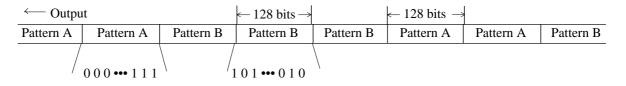

Two patterns, A and B, can be set, and repetition times can be set for each pattern. The data lengths are the same for both patterns.

The following are examples of 128bit patterns:

Pattern A: 0 0 0 ••• 1 1 1 Repetition time: 2 Pattern B: 1 0 1 ••• 0 1 0 Repetition time: 3

Bit 1 of page is set to the head of the pattern.

Note: The FUNCTION switch on the rear of the instrument can be set to switch between patterns A and B by an external signal. In this case, the A/B LOOP TIME display is turned off and the keys of are disabled.

#### **Section 4 OPERATING INSTRUCTIONS**

#### 4.2.3 DATA pattern setting

Select DATA with the keys.

Set DATA LENGTH with the \( \) and \( \) keys.

Select the digit to be set with the **\( \)** keys.

Set DATA LENGTH with the keys.

DATA LENGTH setting steps

2 to 65526: STEP 1 bit 65536 to 131012: STEP 2 bits

See section 1.2, "Functions," for the following.

Set the page that is displayed at the BIT display with the set DATA LENGTH as 16 bits/page. BIT of the displayed page can be changed.

Setting value: 1 to DATA LENGTH/16

(LENGTH is multiple of 16) 1 to INT (DATA LENGTH/16)+1 (LENGTH is not multiple of 16)

Change the BIT value with the button below the LED. When LOGIC is positive, lighting of the LED indicates high level.

Used the PRESET ALL or PAGE key when changing DATA collectively.

PAGE 0 or 1 All BITs of the displayed PAGE are set to 0 or 1.

ALL 0 or 1 Pressing this key holding down the GUARD key sets all BITs specified by DATA LENGTH to 0 or 1.

An optional pattern can be output repetitively. When a 16-bit patern is set:

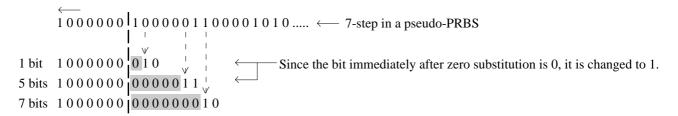

#### 4.2.4 ZERO SUBSTITUTION

Select Z.S. with the \( \) keys.

Set the ZERO SUBSTITUTION BIT LENGTH.

The pattern of bit length logic  $\emptyset$  set here is substituted. See below for the substitution method.

Setting: 1 to  $2^{N}$ -1 (N=7, 9, 11 or 15)

A pattern in which one logical bit is added immediately before the longest string of consecutive 1s of a 7, 9, 11, or 15-step in a pseudo-PRBS (2<sup>N</sup> bits: N=7, 9, 11 or 15) is substituted by an all-0s pattern. If the substituted bit is 0, this 0 is changed to 1.

Example) In the case of a 7-step in a pseudo-PRBS Since the longest string of continuous 0s is 7 - 1 = 6, the zero substitution starts at the next position.

#### **Section 4 OPERATING INSTRUCTIONS**

#### 4.2.5 Pseudo random pattern setting

Select PRBS with the keys.

Set the number of PRBS steps with the keys.

Set the PRBS mark ratio with the keys.

When LOGIC is positive, select the mark ratio from the top row (0/8, 1/8, 1/4, 1/2).

When LOGIC is negative, select the mark ratio from the bottom row (8/8, 7/8, 3/4,  $\overline{1/2}$ ).

If change the logic positive to negative when mark ratio is 1/4, the mark ratio become 3/4.

Patterns generated as explained in Section 5.1 " Pseudo random patern". When an optional continuous N-bit pattern is selected in a PRBS pattern having a  $2^N$  - 1 cycle, all bit paterns in the same cycle we unique. That is, all other bit arrays except all-1s are provided.

Note: When setting pseudo random pattern, the BIT LEDs light according to the set pattern.

#### 4.2.6 ERROR addition

Press the key. The LED in the key lights.

Select the error addition rate with the keys.

To add a single error, select the right of the LED using the key. At this time, the LED does not go on.

The single error adds one error each time the key is pressed. The LED blinks each time a error is added.

Error addition can be inserted for one, and only one, of the 32 routes by using the rotary switch on the rear panel (see below). Therefore, the error multiplied by the output can be added to only one route of the output (1/8 OUTPUT).

Example) When a 1 x  $10^{-4}$  error is added to one channel, following occurs:

1/8 OUTPUT:  $1 \times 10^{-4} \times 8 (= 8 \times 10^{-4})$  error is added to DATA1.

No error is added to DATA2 to DATA8.

The numbers in circles ( ) indicate the output order for 1/8 DATA OUT.

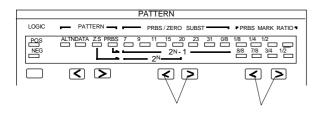

From the above drawing, in 1/8 OUTPUT, if the error insertion channel is 1, 9, 17, or 25, the error is inserted into 1/8 DATAOUT. If the error insertion channel is 5, 13, 21, or 29, the error is inserted into 1/8 DATAOUT 5.

Notes: 1. When the rotary switch is set to channel 00, an error is added to channel 1. When the rotary switch is set to channel 33 to 99, an error is added to channel 32.

2. When the FUNCTION switch on the rear of the instrument is set for external error injection, the error addition amount cannot be changed. However, the error addition ON/OFF key is enabled.

#### **Section 4 OPERATING INSTRUCTIONS**

#### 4.2.7 Tracking

When the key is pressed, the LED inside the key lights and the instrument enters the tracking mode.

\* When tracking, the MP1763B must be connected to an MP1764A by a GPIB.

When the PATTERN LOADING lamp lights, the data is read and the keys are disabled.

Tracking can be performed from both the transmitter and receiver. However, one of them must be set as the master. As a result, tracking cannot be performed concurrently from the transmitter and receiver.

Turn on SYSTEM CONTROL of the Dip switch on the rear of the master instrument to perform tracking. (Turn off SYSTEM CONTROL of the controlled side.)

In addition, set GPIB ADDRESS of the controlled side to GPIB ADDRESS of the master side + 2.

When tracking is on, the setting of the transmitter (or receiver) is changed each time the setting of the receiver (or transmitter) set as the master is changed. Therefore, each time a key is operated on the master side, operation disabled state occurs . (Especially, operation is disabled for more than ten seconds when the bit length of the program is long.) To avoid this condition, turn off tracking before changing the setting of the master side.

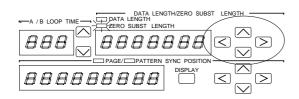

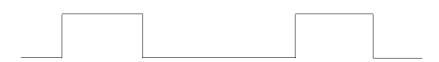

## 4.2.8 Pattern SYNC. position

Select the sync output.

When VARIABLE POSITION is selected, set the SYNC OUT position as described in the following.

1/64 CLOCK, FIXED POSITION, OR VARIABLE POSITION can be selected.

1/64 CLOCK: 1/1 CLOCK is divided by 64.

FIXED POSITION: The sync pulse output fixed on page 1 of VARIABLE POSITION is generated.

VARIABLE POSITION: The sync pulse position is shifted by 16 bits every time the PATTERN SYNC POSITION

value is changed by one. The page numbers are changed by the PRBS step numbers, and all

positions in one cycle can be selected by 16-bit interval.

| PRBS         | Value of PATTERN SYNC POSITION |

|--------------|--------------------------------|

| 27 - 1       | $2^3 = 8$                      |

| 29 - 1       | $2^5 = 32$                     |

| 211 - 1      | $2^7 = 128$                    |

| 215 - 1      | $2^{11} = 2048$                |

| $2^{20}$ - 1 | $2^{16} = 65536$               |

| $2^{23}$ - 1 | $2^{19} = 524288$              |

| $2^{31} - 1$ | $2^{27} = 134217728$           |

|              |                                |

Switch DISPLAY to PATTERN SYNC POSITION, and set the PATTERN SYNC POSITIONS value.

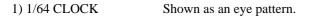

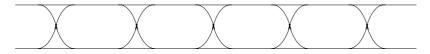

When the PRBS DATA output is monitored on a sampling oscilloscope using each synchronization output, the following waveforms are shown:

2) FIXED POSN Shown as a 0 and 1 waveform. and VAR POSN

\* At VAR POSN, the synchronization position shifts +16 (or -16) bits each time the PAGE/PATTERN SYNC POSITION value is incremented (or decremented) by 1.

- The above figure is an example. Trigger output at the shown position is not specified.

- At FIXED POSN, the position is fixed to 1 of VAR POSN.

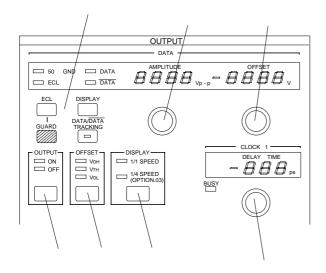

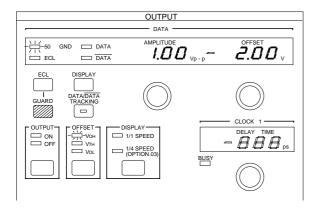

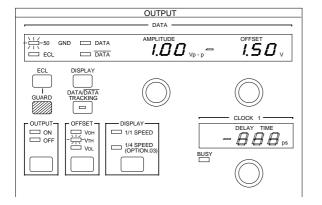

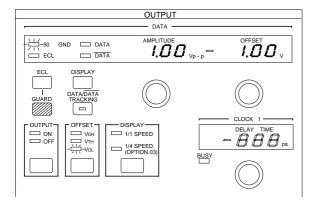

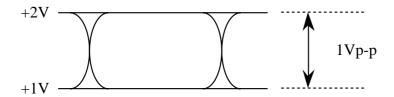

## 4.3 Output Interface

- 1 Termination conditions setting (DATA side)

- 2 DATA/DATA displaying switching and DATA/DATA tracking

- 3 Amplitude (DATA side)

- Offset (DATA side)

- Output ON/OFF

- 6 Offset display standard setting

- 7 1/1 SPEED / 1/4 SPEED display switching

- 8 CLOCK delay

- 9 Termination conditions setting (CLOCK 1 side)

- Amplitude (CLOCK 1 side)

- Offset (CLOCK 1 side)

#### 4.3.1 DUMMY terminal voltage switching

When only CLOCK 1 output is used

When only CLOCK 1 output is used

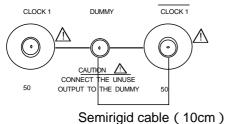

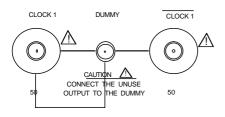

When only one of the CLOCK 1 and CLOCK 1 complementary outputs is used, use the attached semirigid cable (10 cm) to connect the unused side to the DUMMY terminal.

If the termination condition of the side used is 50 , and GND, press the ECL key while holding down the GUARD key of to turn on the 50 GND lamp and set the DUMMY terminal voltage to GND.