# digital

# DIGITAL Semiconductor EBSA-285 Evaluation Board

# **Reference Manual**

Order Number: EC-R6M5B-TE

The EBSA-285 is an evaluation board for the SA-110 StrongARM® microprocessor and the 21285 Core Logic controller. The evaluation board is a PCI card that can be used in various configurations.

This manual is the single point of reference for all users of the EBSA-285. It describes how to install the card and power it up for the first time. It also acts as a configuration guide, a programmer's guide, and a technical reference.

**Revision/Update Information:** This is a revised document. It supercedes the *DIGITAL Semiconductor EBSA-285 Evaluation Board Reference Manual*, EC–R6M5A–TE.

Digital Equipment Corporation Maynard, Massachusetts

http://www.digital.com/semiconductor

#### October 1997

While DIGITAL believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

#### Warning!

This is a Class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

#### Achtung!

Dieses ist ein Gerät der Funkstörgrenzwertklasse A. In Wohnbereichen können bei Betrieb dieses Gerätes Rundfunkstörungen auftreten, in welchen Fällen der Benutzer fur entsprechende Gegenmaßnahmen verantwortlich ist.

#### Attention!

Ceci est un produit de Classe A. Dans un environnement domestique, ce produit risque de créer des interférences radioélectriques, il appartiendra alors à l'utilisateur de prendre les mesures spécifiques appropriées.

This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of FCC rules, which are designed to provide reasonable protection against such radio frequency interference.

Operation of this equipment in a residential area may cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Any modifications to this device - unless expressly approved by the manufacturer - can void the user's authority to operate this equipment under part 15 of the FCC rules.

©Digital Equipment Corporation 1997. All rights reserved. Printed in U.S.A.

DIGITAL, DIGITAL Semiconductor, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

DIGITAL Semiconductor is a Digital Equipment Corporation business.

ARM is a registered trademark and StrongARM is a trademark of Advanced RISC Machines Ltd. Cypress is a trademark of Cypress Semiconductor Corporation. Intel and Pentium Pro are registered trademarks of Intel Corporation. PostScript is a registered trademark of Adobe Systems Incorporated. PROMJet is a registered trademark of EmuTec Inc. QuickSwitch is a registered trademark of Quality Semiconductors, Inc. Samsung is a trademark of Samsung Electronics America, Inc. Viewlogic is a registered trademark of Viewlogic Systems, Inc. Windows is a registered trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective owners.

# Contents

### Preface

# 1 Getting Started

| 1.1   | Physical Description                 | 1-1  |

|-------|--------------------------------------|------|

| 1.2   | Unpacking the Card                   | 1-2  |

| 1.3   | Understanding the Different Modes    | 1-3  |

| 1.3.1 | Add-in Card                          | 1-4  |

| 1.3.2 | Host Bridge                          | 1-5  |

| 1.3.3 | Example Installation                 | 1-5  |

| 1.3.4 | Other Configuration Options          | 1-6  |

| 1.4   | Powering Up for the First Time       | 1-7  |

| 1.5   | Running the Onboard Diagnostics      | 1-8  |

| 1.6   | Using the ARM SDT with your EBSA-285 | 1-8  |

| 1.7   | Support for Angel Over the Ethernet  | 1-9  |

| 1.7.1 | Description                          | 1-10 |

| 1.7.2 | Low-Level Angel Interface            | 1-11 |

| 1.7.3 | Initialization                       | 1-11 |

| 1.7.4 | Host/Client Interaction              | 1-11 |

| 1.7.5 | Areas of Difference                  | 1-12 |

# 2 Functional Specification

| 2.1   | CPU                  | 2-1 |

|-------|----------------------|-----|

| 2.2   | 21285                | 2-1 |

| 2.3   | The Memory Subsystem | 2-2 |

| 2.3.1 | SDRAM                | 2-3 |

| 2.3.2 | Flash ROM.           | 2-3 |

| 2.3.3 | EPROM Emulator       | 2-4 |

| 2.3.4 | Memory-Map Switching | 2-5 |

| 2.4   | I/O Subsystem        | 2-5 |

| 2.5  | Interrupts               | 2-5  |

|------|--------------------------|------|

| 2.6  | PCI Interface            | 2-5  |

| 2.7  | PCI Bus Arbiter          | 2-6  |

| 2.8  | JTAG                     | 2-6  |

| 2.9  | Expansion                | 2-9  |

| 2.10 | Clocks                   | 2-9  |

| 2.11 | Resets                   | 2-9  |

| 2.12 | Power Requirements       | 2-10 |

| 2.13 | Onboard Power Generation | 2-10 |

| 2.14 | Onboard Software         | 2-10 |

# 3 Programmer's Guide

| 3.1 | Flash Memory                  | 3-1 |

|-----|-------------------------------|-----|

|     | SDRAM Memory                  | 3-2 |

| 3.3 | X-Bus Memory-Map              | 3-2 |

| 3.4 | Interrupt Assignment          | 3-2 |

| 3.5 | Timer Assignment              | 3-3 |

| 3.6 | Soft Input/Output Register    | 3-3 |

| 3.7 | The Reset State of the System | 3-5 |

# 4 Software Configuration and Initialization

| 4.1   | Disabling the Flash ROM Alias                | 4-1 |

|-------|----------------------------------------------|-----|

| 4.2   | Accessing the Flash ROM                      | 4-2 |

| 4.2.1 | Programming the Flash from the SA-110        | 4-2 |

| 4.2.2 | Programming the Flash from the PCI Interface | 4-2 |

| 4.3   | Determining the Card Configuration           | 4-3 |

| 4.4   | Initializing the X-Bus                       | 4-3 |

| 4.5   | Initializing the PCI Bus Arbiter             | 4-3 |

| 4.6   | Setting the INITIALIZE_COMPLETE Bit          | 4-3 |

| 4.7   | Initializing the SDRAM                       | 4-4 |

| 4.8   | Re-initializing the SDRAM                    | 4-6 |

| 4.9   | Initializing the PCI Interface               | 4-7 |

| 4.10  | Initializing the 21285 UART                  | 4-8 |

| 4.11  | Configuring Cacheable/Non-Cacheable Space    | 4-9 |

#### 5 Software Development Environment

| 5.1     | Loadable Debuggable Images | 5-1 |

|---------|----------------------------|-----|

| 5.1.1   | Building                   | 5-1 |

| 5.1.2   | Run-Time Environment       | 5-2 |

| 5.1.2.1 | Memory Map                 | 5-2 |

| 5.1.2.2 | ARM C Library Support      | 5-2 |

| 5.1.2.3 | Exception Vectors          | 5-2 |

| 5.1.2.4 | Access to I/O Devices      | 5-2 |

| 5.2     | Standalone Flash Images    | 5-3 |

| 5.2.1   | Building                   | 5-3 |

| 5.2.2   | Run-Time Environment       | 5-4 |

| 5.2.2.1 | Метогу Мар                 | 5-4 |

| 5.2.2.2 | C Library Support          | 5-4 |

| 5.2.2.3 | Exception Vectors.         | 5-4 |

| 5.2.2.4 | Access to I/O Devices      | 5-4 |

### 6 Onboard Software

| 6.1   | Primary Boot Loader              | 6-1 |

|-------|----------------------------------|-----|

| 6.2   | Format of Images in Flash ROM    | 6-2 |

| 6.3   | Angel                            | 6-4 |

| 6.4   | Diagnostics                      | 6-4 |

| 6.4.1 | Preparing to Run the Diagnostics | 6-4 |

| 6.4.2 | Description of Tests             | 6-5 |

#### 7 Flash Management Utility

| 7.1   | Using the FMU                       | 7-1 |

|-------|-------------------------------------|-----|

| 7.1.1 | When to Specify the Block Number    | 7-4 |

| 7.1.2 | When to Specify the 'NoBoot' Option | 7-5 |

### 8 Theory of Operation/Hardware Design

| 8.1 | General                           | 8-1 |

|-----|-----------------------------------|-----|

| 8.2 | An Introduction to the Schematics |     |

| 8.3 | Voltage Domains                   | 8-2 |

| 8.4 | Interfacing Techniques            | 8-3 |

|     | Principal Buses                   |     |

|     | CPU                               | 8-4 |

| 8.7 | 21285                             | 8-5 |

| 8.8      | SDRAM Interface           | 8-5 |

|----------|---------------------------|-----|

| 8.8.1    | Multiplexed Address Bus   | 8-6 |

| 8.8.2    | Bank Address Bus          | 8-6 |

| 8.8.3    | Data Bus                  | 8-6 |

| 8.8.4    | CMD                       | 3-6 |

| 8.8.5    | Chip Selects              | 8-7 |

| 8.8.6    |                           | 8-7 |

| 8.8.7    | DIMMs                     | 3-7 |

| 8.9      | Flash ROM Interface       | 8-9 |

| 8.10     |                           | ·10 |

| 8.10.1   | Soft I/O                  | -10 |

| 8.10.2   | X-Bus Expansion Headers   | -11 |

| 8.11     | The Serial Port           | -11 |

| 8.12     |                           | ·12 |

| 8.13     | PCI Interface             | ·12 |

| 8.14     | PCI Bus Arbiter           | ·13 |

| 8.15     | JTAG                      | 14  |

| 8.16     | Clocks                    | 14  |

| 8.17     | Reset                     | -15 |

| 8.17.1   | Host Bridge               | 15  |

| 8.17.1.1 | Power-On Reset            | 16  |

| 8.17.1.2 | Switch Reset              | 16  |

| 8.17.1.3 | JTAG Connector Reset 8-   | -16 |

| 8.17.1.4 | Watch Dog Timer Reset 8-  | ·17 |

| 8.17.1.5 | PCI Reset                 | ·17 |

| 8.17.2   | Add-in Card               | ·17 |

| 8.17.2.1 | PCI Master Reset          | ·17 |

| 8.17.2.2 | Blank Programming Mode8-  | ·17 |

| 8.18     | Power                     | ·18 |

| 8.18.1   | 3.3-V Generation          | ·18 |

| 8.18.2   | 2.0-V Generation          | 19  |

| 8.18.3   | Power Sequencing          | ·19 |

| 8.19     | Decoupling                | ·19 |

| 8.20     |                           | ·19 |

| 8.21     | Expanding the EBSA-285    | 20  |

| 8.22     | The Printed Circuit Board | -20 |

| 8.23     | Design Improvements       | -21 |

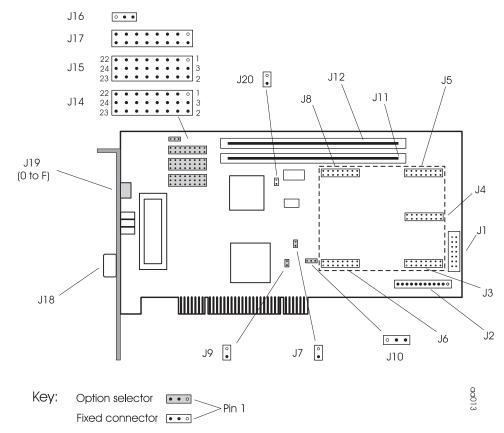

## A Configuration Guide

| A.1     | Default Configuration                          | A-2  |

|---------|------------------------------------------------|------|

| A.2     | Description of Jumpers and Connectors          | A-5  |

| A.2.1   | X-Bus Expansion Headers                        | A-5  |

| A.2.2   | Configuration Jumpers                          | A-7  |

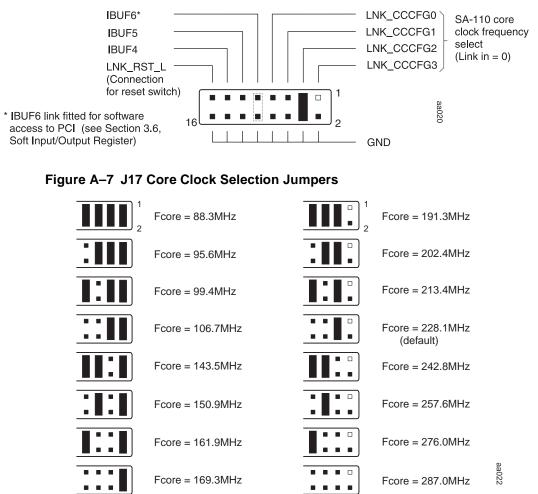

| A.2.2.1 | CPU Core Clock Frequency Selection             | A-7  |

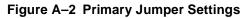

| A.2.2.2 | Arbiter/X-Bus Selection                        | A-9  |

| A.2.2.3 | Flash/EPROM Selection                          | A-10 |

| A.2.2.4 | Selection of the 21285 as the Central Function | A-11 |

| A.2.2.5 | Reserved Mode                                  | A-12 |

| A.2.2.6 | Boot Image Selection                           | A-12 |

| A.2.2.7 | SA-110 Clock Probe Connection                  | A-12 |

| A.2.2.8 | Test Points                                    | A-13 |

| A.3     | Connectors                                     | A-13 |

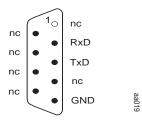

| A.3.1   | Serial Port Connector                          | A-13 |

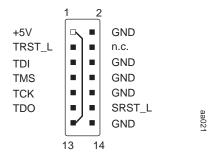

| A.3.2   | JTAG Connector                                 | A-13 |

| A.3.3   | Power Connector                                | A-14 |

| A.4     | Cables for External Connection                 | A-14 |

| A.4.1   | Serial Port                                    | A-14 |

| A.4.2   | JTAG Port                                      | A-15 |

| A.5     | Upgrading the SDRAM DIMMs                      | A-16 |

#### B The Design Database

| B.1 | Hardware Material | B-1 |

|-----|-------------------|-----|

| B.2 | Software Material | B-2 |

#### C Support, Products, and Documentation

### Index

# Figures

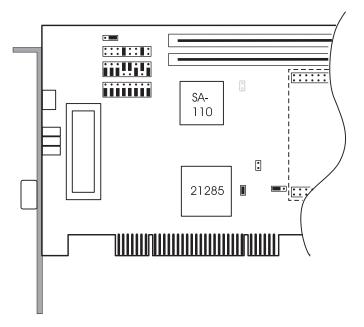

| 1–1  | EBSA-285                                                          | 1-2  |

|------|-------------------------------------------------------------------|------|

| 1–2  | Example Configuration in an EBSA-BPL-5V or EBSA-BPL-3V3 Backplane | 1-6  |

| 1–3  | Angel Communication Overview                                      | 1-10 |

| 2–1  | EBSA-285 Block Diagram                                            | 2-2  |

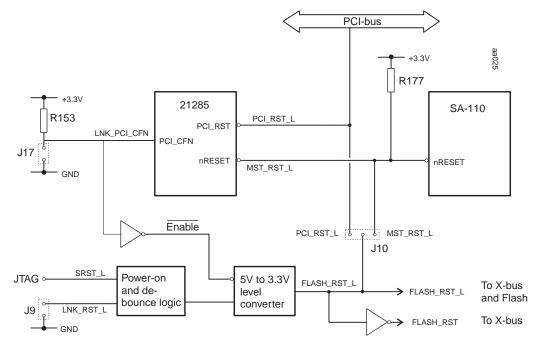

| 8–1  | Reset Circuits                                                    | 8-15 |

| A–1  | Jumper and Connector Locations                                    | A-2  |

| A–2  | Primary Jumper Settings                                           | A-3  |

| A–3  | EBSA-285 Configured as an Add-in Card.                            | A-4  |

| A–4  | EBSA-285 Configured as a Host Bridge                              | A-4  |

| A–5  | X-Bus Headers Pinout                                              | A-6  |

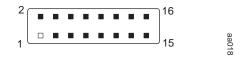

| A–6  | J17 Pinout Showing Default Jumper Configuration.                  | A-8  |

| A–7  | J17 Core Clock Selection Jumpers                                  | A-8  |

| A–8  | J14/J15 Pinout                                                    | A-9  |

| A–9  | Serial Port Connector Detail                                      | A-13 |

| A–10 | JTAG Connector J1 Pinout                                          | A-14 |

### Tables

| 2–1  | TAP IDC Connector Pinout                               | 2-6  |

|------|--------------------------------------------------------|------|

| 2–2  | Signals on the TAP                                     | 2-7  |

| 2–3  | JTAG Registers                                         | 2-7  |

| 2–4  | JTAG Commands                                          | 2-8  |

| 3–1  | Interrupt Assignment                                   | 3-2  |

| 3–2  | Bit Assignment of Soft Input/Output Register           | 3-4  |

| 4–1  | 21285 Baud Rate Divisors for 50 MHz fclk_in.           | 4-8  |

| 6–1  | Boot Image Selection                                   | 6-2  |

| 6–2  | Flash Image Header                                     | 6-3  |

| 8–1  | SDRAM Array Configuration: 2-Array Part                | 8-8  |

| 8–2  | SDRAM Array Configuration: 4-Array Part                | 8-8  |

| 8–3  | Use of Reserved PCI Pins                               | 8-13 |

| A–1  | General Information on EBSA-285 Jumpers and Connectors | A-5  |

| A–2  | X-Bus Connector J3                                     | A-6  |

| A–3  | X-Bus Connectors J4/J5                                 | A-6  |

| A–4  | X-Bus Connector J6                                     | A-7  |

| A–5  | X-Bus Connector J8                                     | A-7  |

| A–6  | Arbiter/X-Bus Selection Jumpers                        | A-9  |

| A–7  | Flash/EPROM Socket Selection                           | A-10 |

| A–8  | Flash/EPROM Socket Selection (J16)                     | A-11 |

| A–9  | Jumper Combinations for ROM Selection                  | A-11 |

| A–10 | Selection of Central Function                          | A-11 |

| A–11 | Jumper Settings for Selection of Central Function      | A-12 |

| A–12 | Description of Test Points                             | A-13 |

| A–13 | Null-Modem Cable                                       | A-15 |

| A–14 | Sun Null-Modem Cable                                   | A-15 |

| A–15 | JTAG Cable                                             | A-16 |

| A–16 | DIMMs For Use With The EBSA–285                        | A-17 |

|      |                                                        |      |

# Preface

#### Introduction

The EBSA-285 is an evaluation board for DIGITAL Semiconductor's SA-110 microprocessor and 21285 Core Logic controller. It is designed to:

- Provide a software test and debug environment.

- Allow benchmarking of prototype software algorithms.

- Act as a reference platform for operating system ports.

- Demonstrate the performance of the 21285's PCI interface, memory controller and internal functional blocks.

- Provide a building block that can be used to build software-accurate models of target applications.

- Act as a proven hardware design that can be modified for use in other applications.

- Allow all the major features of the 21285 to be demonstrated and tested.

This document is a single point-of-reference both for configuring and using the board and for engineers wishing to copy parts of its design. As such, it has the following scope:

- Functional specification

- Theory of operation (to be read in conjunction with the circuit schematics)

- Configuration guide (memory options, speed options, jumper and link options)

- Programmers' guide (memory maps, boot process, references to programmable I/O devices on the board)

This document aims not to duplicate material that can be found elsewhere. Specifically, it does not duplicate material that can be found in vendor data sheets for components used in the design, nor does it document the ARM software development environment.

## How to Use This Document

All readers should turn to Chapter 1 for information about how to connect and power on the board, how to verify that it is working correctly, and how to connect it to a terminal or host system.

All readers are advised to read Chapter 2 to get an understanding of the overall functionality of the board. Subsequent chapters assume a familiarity with the material in that chapter.

Thereafter, software engineers will probably want to refer to the following chapters:

- Chapter 3 is a guide to the memory map of the board and the address decoding of all I/O devices.

- Chapter 4 is a guide to configuration of the memory and other devices on the board.

- Chapter 5 is a brief introduction to the software development environment.

- Chapter 6 describes the onboard software, including the power-on sequence of the board, and the power-on diagnostics.

- Chapter 7 describes the Flash Management Utility that is provided with the EBSA-285.

Hardware engineers will probably want to refer to the following chapters:

• Chapter 8 is a detailed technical description of the hardware of the card, including the theory of operation.

A number of appendixes provide general reference material:

- Appendix A describes all of the link and jumper options present on the card, and all of the cables that may be required for connection to the card.

- Appendix B describes the machine-readable design databases for the EBSA-285 hardware and software.

- Appendix C identifies other relevant documents and services that are available from DIGITAL and its partners.

# Notation

All numbers are shown in decimal unless otherwise stated.

All hexadecimal numbers have an 0x prefix. 32-bit hex values have dots for ease of reading. Examples are: 0xfe0b.3004, 0xfb.

All binary number have an 0b prefix; long numbers include dots for ease of reading. Examples are: 0b00, 0b0000.0000.1010.0000.

This document refers to an 8-bit data unit as a byte, a 16-bit data unit as a half-word and a 32-bit data unit as a longword.<sup>1</sup>

Electrical signal names are shown thus: **cpu\_wait\_l**. An **\_l** at the end of a signal name indicates that the signal is asserted (active) when it is low (close to 0V).

Displayed messages are printed in 9-point Courier format. For example: Test Passed

# References

This section provides a selective bibliography and a reference to relevant manufacturers' data sheets. ARM-specific and SA-110-specific information is referenced in Appendix C.

<sup>1</sup> Standard ARM notation is to use the terms byte, half-word and word, respectively. DIGITAL's convention is to use the terms byte, word and longword. Therefore, this document avoids use of the term 'word', which is ambiguous to different audiences.

- 1. *High-Speed Digital Design* a handbook of black magic. (Howard W Johnson, Martin Graham, 1993 Prentice Hall ISBN 0-13-395724-1)

- 2. Intel 28F008 data sheet (visit http://developer.intel.com)

- 3. Samsung *1996 16M Sync DRAM* databook

# **1** Getting Started

The EBSA-285 is supplied as a plug-in card. This chapter provides a physical description of the card and then describes:

- How to unpack the card and give it a visual inspection

- The different modes that the card can be used in

- How to configure the card to suit your application

- How to power up the card for the first time

- How to connect the card to a host system and run its onboard diagnostics

# **1.1 Physical Description**

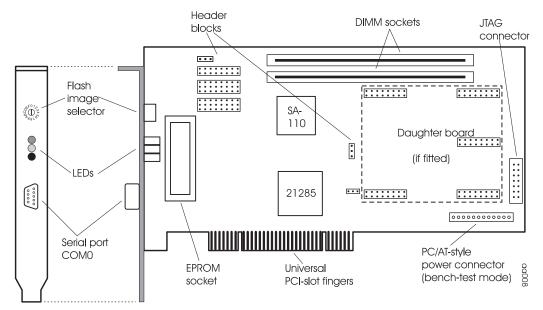

The physical layout of the EBSA-285 is shown in Figure 1-1. It is a single-board computer with the form-factor of a PCI add-in card.

The EBSA-285 contains processor, system controller, memory and input/output devices. There are a number of header blocks on the card that accept 2-pin jumpers, allowing the card to be configured in different ways, so that all of the major features of the 21285 can be used.

The bulkhead mounting bracket of the EBSA-285 holds a female 9-way D-type connector, three LED indicators and a rotary switch. The D-type connector provides an RS232 terminal connection to a host system. The LEDs provide status information during power up and self-test. The rotary switch is used by onboard software to allow a particular image stored on the board to be executed automatically at power up.

#### **Unpacking the Card**

#### Figure 1–1 EBSA-285

## 1.2 Unpacking the Card

- **Caution:** The EBSA-285 contains electronic components that are susceptible to permanent damage from electrostatic discharge (static electricity). To prevent electrostatic damage it is supplied in an antistatic bag. When handling the card, risk of damage can be alleviated by following a few simple precautions:

- Do not remove the card from the bag unless you are working on an antistatic, earthed surface and wearing an earthed antistatic wrist strap.

- Keep the antistatic bag that the card was supplied in; if you remove the card from a system, store it back in the bag.

The EBSA-285 is normally supplied with a single, 168-pin plug-in DIMM module containing 16 MB of SDRAM memory. If the DIMM is not fitted when you receive your EBSA-285, install it by following these steps:

1. Identify the DIMM socket closest to the edge of the EBSA-285.

- 2. Slide the DIMM into the socket taking account of the polarity slots. Do not touch the gold contacts. You can see that there are two polarization slots cut in the DIMM; this ensures that the DIMM is oriented correctly.

- 3. Support the underside of the EBSA-285 and press the DIMM down into the socket. It should mate with a gentle 'click'.

Before you install and power up your EBSA-285, you should perform a quick visual inspection:

- 1. Inspect the card for physical damage.

- 2. Ensure that each of the 2-pin jumpers is pushed down firmly onto its mounting posts. If you remove any of the jumpers, refer to Appendix A to ensure they are replaced correctly.

- 3. Ensure that one DIMM is fitted, in the socket closest to the edge of the card, and that the main portion of the gold contacts on the DIMM has disappeared into the socket along the whole length of the DIMM.

- 4. Check the position of the Flash Image selector switch. There is a dot or an arrow on the switch showing which image is selected. If necessary, use a small screw-driver to rotate the switch so that image 0 is selected.

# **1.3 Understanding the Different Modes**

There are two distinct ways in which the EBSA-285 can be configured. In order to understand the differences between them, it is necessary to review some aspects of the architecture of a PCI-based system.

The PCI bus has a multi-master capability, allowing any PCI master in the system peer-to-peer access to any other PCI master/target.

In general, the PCI bus is symmetrical, so that any device on the bus can have the same set of capabilities as any other device. However, one device in the system is responsible for generating a software-driven initialization and configuration of all devices on the bus after power up or reset.

Initialization and configuration is performed using Configuration Cycles on the PCI bus and the device that interfaces to the PCI bus to perform these cycles is called the Host Bridge. The processor that accesses the PCI bus through the Host Bridge is called the host processor, or simply the host.

In this document, all devices on the PCI other than the Host Bridge are referred to as PCI devices or add-in cards, or agents.

#### **Understanding the Different Modes**

In a motherboard-based system like a PC, the host processor and the Host Bridge are built onto the motherboard. The motherboard may also contain some PCI devices (for example, an Ethernet network interface) and further PCI add-in cards may be plugged into PCI expansion connectors on the motherboard.

The EBSA-285 can act either as a Host Bridge (in which case the EBSA-285's SA-110 processor is the host processor) or as an add-in card (in which case the SA-110 processor would normally be termed a co-processor).

The 21285 is configured in a mode called 'Central Function' (CFN) mode when it is acting as the Host Bridge for a system.

In addition to the generation of PCI configuration cycles, there are a number of other functions that are normally associated with the Host Bridge:

- Bus arbitration

- PCI clock generation

- Interrupt controller

- Reset generation

- The provision of pullups or 'keepers' on some bus signals

Some of these functions are referred to in the PCI specification as 'Central Resource Functions'.

#### 1.3.1 Add-in Card

This is the default mode for the card. When you receive a new EBSA-285, the jumpers on the card will be configured for this mode.

If you already own a PC with a PCI expansion bus then using this mode is the simplest way to power up and use the EBSA-285.

When the EBSA-285 is configured in this mode it can be plugged into an existing PC motherboard or into a PCI backplane which already contains a Host Bridge. The EBSA-285 is supplied with power, reset and PCI clock from the PCI connector. The motherboard or PCI backplane provides bus arbitration, interrupt controller and pullups for the system.

When the host system is powered up, software running on the host processor will read the configuration registers of the 21285 on the EBSA-285 and allocate system resources for it accordingly. On a standard PC, this function is performed by the BIOS.

#### 1.3.2 Host Bridge

This is *not* the default mode for the card. When you receive a new EBSA-285, refer to Appendix A to configure the jumpers on the card for correct operation in this mode.

When the EBSA-285 is configured in this mode it must be plugged into a special slot (the 'System' or 'Host' slot) in a PCI backplane. DIGITAL can supply the EBSA-BPL-5V and EBSA-BPL-3V3 as suitable backplanes. The EBSA-285 acts as the Host Bridge and also provides the PCI interrupt controller for the system. It is supplied with power and PCI clock from the backplane. The EBSA-BPL backplane also provides PCI bus arbitration and pullups.

If you wish to use a PCI backplane other than the EBSA-BPL-5V/EBSA-BPL-3V3, refer to *DIGITAL Semiconductors EBSA–BPL Reference Manual* to confirm that the backplane is suitable before powering up for the first time.

#### 1.3.3 Example Installation

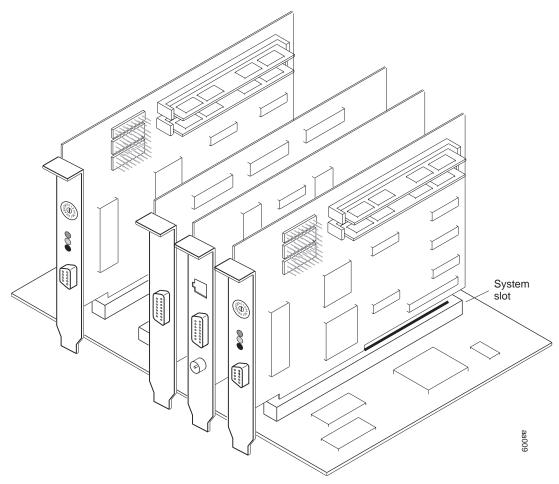

Figure 1–2 shows an advanced installation using the EBSA-285 and one of the DIGITAL Semiconductor PCI Development Backplanes.

In this arrangement there are two EBSA-285 cards, a PCI network card and a PCI video card. The EBSA-285 in the backplane's System slot is configured as a Host Bridge and the other EBSA-285 is configured as an add-in card.

#### **Understanding the Different Modes**

Figure 1–2 Example Configuration in an EBSA-BPL-5V or EBSA-BPL-3V3 Backplane

#### **1.3.4 Other Configuration Options**

The EBSA-285 also supports configuration options that are beyond the scope of this introductory section. These include:

- Setting the SA-110 processor core frequency

- Using the 21285 internal PCI arbiter instead of the backplane arbiter (only applicable in Host Bridge mode)

- Allowing a plug-in EPROM emulator to be used in place of the onboard flash ROM

• Holding the SA-110 processor in reset so that a new image can be programmed into the onboard flash ROM (only applicable in add-in card mode)

Refer to Appendix A for details on selecting and using these modes.

# 1.4 Powering Up for the First Time

Use Section 1.3 to decide which mode to use your card in, and use Appendix A to ensure the jumpers are set appropriately. If you need more details on how to install the card or attach a power supply, refer to Appendix C.

Use an RS232 null-modem cable to attach the COM0 port on the EBSA-285 to an RS232 port on a terminal or terminal emulator. For example, you could connect to a PC running Windows and use the Windows Terminal or Hyperterminal application. Configure the terminal to operate at 9600 baud, 8-bit data, 1 stop bit, no parity, no flow control. If you need more details on choosing an appropriate cable, refer to Appendix A.

**Note:** If you are using the card as an add-in card, you cannot use a terminal emulator running on the host for this initial test because the card will have issued messages before the host has booted.

Identify the group of three LEDs on the bulkhead mounting bracket of the EBSA-285. Power-cycle the system and watch the LEDs.

The LEDs should all be illuminated initially and then be extinguished after about half a second. At the same time, the terminal screen should display a message similar to this:

Angel Debug Monitor for EBSA 285 (FIQ), MMU off, Clock Switching on (serial)

1.00 (Advanced RISC Machines 2.11) rebuilt on Jun 9 1997 at 23:57:00

If you fail to see the behavior described then use this checklist to identify the problem:

- If you have configured the EBSA-285 as an add-in card and it stops the host PC from booting correctly, verify the jumper settings on the card.

- If the LEDs behave correctly but the terminal doesn't produce any output, check the terminal cable and terminal settings. You can test the cable by connecting it between two PC COM ports and running terminal emulation on each port; if the cable is correctly wired you will be able to type characters on either terminal emulator and display them on the other.

- If neither the LEDs nor the terminal behaves correctly then check that the jumpers are set correctly and that the flash image selector switch is set to 0.

- Attempt to run the onboard diagnostics by following the instructions in the next section.

# 1.5 Running the Onboard Diagnostics

You can get an additional level of confidence that the card is working correctly by running the onboard diagnostics that are programmed into the flash ROM.

Before starting the diagnostics:

- 1. Attach the card to a terminal as described in Section 1.4.

- 2. Use a small screwdriver to rotate the Flash Image selector switch so that the dot or arrow on the switch points to the number 1. This selects the image that, by default, contains the onboard diagnostics.

- 3. Power-cycle the system. The diagnostics should start up automatically and report progress on the terminal. The first thing that the diagnostics do is to flash all three LEDs once.

Chapter 6 describes the output that the diagnostics should produce and describes what to do if the diagnostics fail.

# 1.6 Using the ARM SDT with your EBSA-285

The ARM Software Development Toolkit (SDT) includes a remote debugger. When running the remote debugger, one part runs on the host (this part includes the user interface) and the other part runs on the target (the EBSA-285). The host and target communicate across a communications channel. By default, the EBSA-285 uses its COM0 RS232 port to communicate with the host.

The software that runs on the Target is called the *remote debug agent* or *remote debug stub*. By default, the remote debug agent used with the EBSA-285 is a program called Angel.

Use an RS232 null-modem cable between the COM0 port on the EBSA-285 and the RS232 port on the machine on which the SDT has been installed.

If you are using the EBSA-285 as an add-in card, the SDT can run on the same host. This requires COM0 to be connected to one of the COM ports on the host.

Start up the ARM debugger in the SDT. Use the 'remote\_a' option from the options menu to select remote debug across a serial port.

For more details on using the SDT, refer to the *ARM Software Development Toolkit Reference Manual*. Chapter 6 describes how to use the SDT to build images that can be executed and debugged on the EBSA-285.

# 1.7 Support for Angel Over the Ethernet

A TCP/IP Ethernet stack has been added to the Angel debugger for faster downloads and debugging of programs targeted for the EBSA-285. The system requires a Bootp server to be running on the Ethernet to which the EBSA-285 is connected, for it to resolve its own IP address. Beyond this the differences, other than download speed, between using the ARM debugger over serial and Ethernet are largely transparent.

For a description of IP stacks and the general terminology please refer to, *Internetworking with TCP/IP, Principles, Protocols and Architecture*. Author: Douglas Comer. ISBN: 0-13-470188-7

#### Support for Angel Over the Ethernet

#### 1.7.1 Description

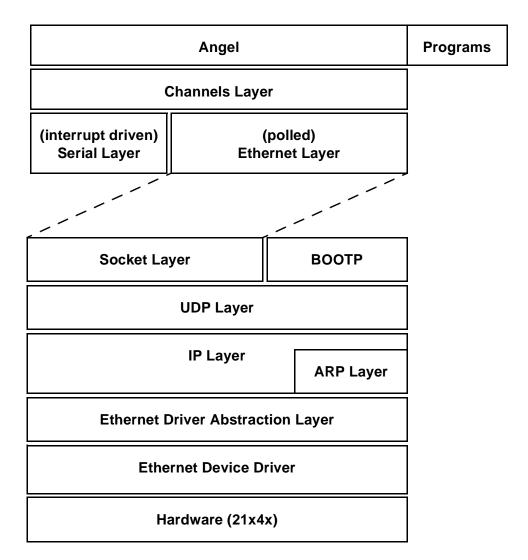

#### Figure 1–3 Angel Communication Overview

Figure 1–3 shows the layers involved with communications over the Ethernet, and how Angel and user program relate. The program communicates its print/read statements and semi-hosting commands via Angel, just as for serial. The channels layer

within Angel then decides which is the active device and uses that device to send the message to the debugging host. The stack is a minimal implementation to satisfy the needs of Angel only.

#### 1.7.2 Low-Level Angel Interface

The area of interaction between Angel and the stack is via a socket layer interface. This is a minimal implementation of a socket layer, allowing use of:

| Socket   | - Initialize a socket                 |

|----------|---------------------------------------|

| bind     | - Bind socket to a port               |

| sendto   | - Send to a specific address          |

| recv     | - Receive                             |

| recvfrom | - Receive and indicate source of data |

| close    | - Close the socket                    |

All of the options and flags in these functions are ignored.

#### 1.7.3 Initialization

Upon initialization the stack will attempt to find out its own IP address using the bootp protocol. It will send out four bootp requests, approximately one to two seconds apart, but will stop when it receives a valid reply. If no bootp request is received then only serial will be usable. A broadcast message is sent to indicate that the debugger is ready to connect when the bootp is complete.

**Note:** During this bootp period it will not be possible to connect to the debugger.

#### 1.7.4 Host/Client Interaction

Angel will now poll the Ethernet stack and listen for the host debugger trying to connect. The communications occur over UDP/IP, the Angel connect happens on a known port. When a packet with a 'magic' word is received on this known UDP port it initiates a negotiation of other communication channels and various Angel parameters. The host may also connect via serial, in which case the Ethernet stack is no longer polled.

Angel can now communicate with the host over the negotiated channels. The ARM remote debugger usage from this point should be the same as for serial debugging. However, it should be noted that Angel must be allowed to run occasionally in order

#### Support for Angel Over the Ethernet

for it to examine the Ethernet stack – this is entirely dependent upon the application that is being run calling 'angel\_yield' from time to time. This is not necessary for serial because serial uses interrupts to transfer data so is able to halt the application in the foreground. It is not detrimental to yield when serial is being used. Although there is a method built into Angel to start the polling mechanism, polling is always controlled by the program.

Packet transmission via Ethernet is immediate.

#### 1.7.5 Areas of Difference

The stack requirements are different. Angel uses more stack because of the layered approach to IP - see devconf.h for the sizes.

# 2

# **Functional Specification**

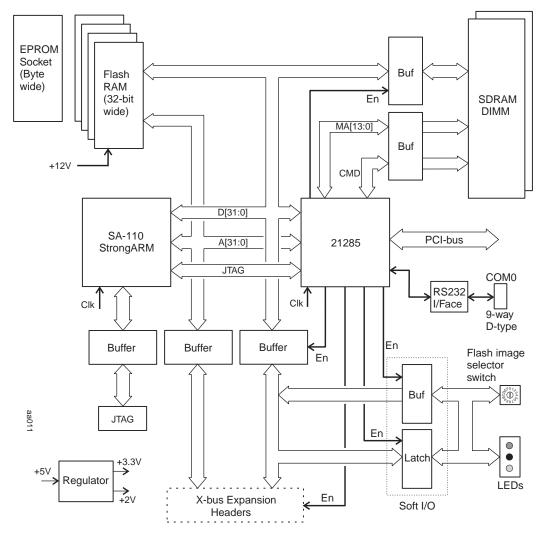

This chapter describes each functional element of the EBSA-285. More detailed information describing how the board works and how to program it can be found in later chapters of this document. Figure 2–1 is a basic block diagram of the board, showing how the major elements interconnect.

# 2.1 CPU

The EBSA-285 uses the SA-110 microprocessor as its CPU. The board allows the processor to be operated at any one of its 16 core clock frequencies (between 88.3 MHz and 287 MHz with the upper limit determined by the speed grade of the CPU fitted) at a fixed core voltage of 2.0 V.

The CPU is packaged in a 144-pin thin quad flat pack (TQFP).

# 2.2 21285

The 21285 is a Core Logic controller for the SA-110 microprocessor. The 21285 performs all of the control functions on the EBSA-285.

The 21285 is packaged in a 256-point plastic ball grid array (BGA).

#### The Memory Subsystem

Figure 2–1 EBSA-285 Block Diagram

## 2.3 The Memory Subsystem

The EBSA-285 provides synchronous DRAM (SDRAM) for its main memory and flash ROM for its boot path and non-volatile storage. It also supports the use of a plug-in ROM emulator to aid software debug.

#### 2.3.1 SDRAM

SDRAM chips usually contain multiple logical banks of memory (typically 2 or 4) within a single chip. The existence of these multiple banks is invisible to software but allows the memory controller to extract greater performance from the memories. To avoid confusion with these internal banks, the term *array* is used to describe a physical group of memory devices that share a common chip select and provide a 32-bit data path.

The 21285 supports four SDRAM arrays.

The EBSA-285 has sockets for two 168-pin 64-bit SDRAM DIMMs. The 64-bit data path of the DIMM is treated as two separate arrays (since the 21285 requires a 32-bit data path).

One of the sockets can accommodate a DIMM of up to four arrays, the other can accommodate a DIMM of up to two arrays.

The standard configuration of the EBSA-285 contains a single 2-array DIMM, providing a total of 16 MB of memory.

Section A.5 explains how to choose suitable DIMMs with which to upgrade the EBSA-285.

#### 2.3.2 Flash ROM

Non-volatile storage is provided by four byte-wide 1-MB flash ROMs, arranged to provide a 32-bit ROM path. This provides a total of 4 MB of ROM.

The ROM is used for two purposes:

- In all configurations of the EBSA-285 it provides the boot code for the SA-110.

- When the EBSA-285 is used as an add-in card, the SA-110 software can make a region of the ROM visible on the PCI bus so that it appears in PCI space as a PCI expansion ROM. The expansion ROM makes code available to the host processor that can be executed for device-specific initialization and, possibly, a system boot function.

The 21285 supports 8-bit, 16-bit and 32-bit ROMs, but the EBSA-285 design only allows the 32-bit mode to be used for accesses to the flash ROM.

The flash ROM is divided into a number of separate blocks, which can be erased and reprogrammed independently. The EBSA-285 is supplied with code programmed into some of the flash blocks. In particular, block 0 of the flash contains the bootstrap code for the SA-110, including the remote debug agent.

If block 0 becomes corrupt, the SA-110 will be unable to execute code after a reset. In this situation, the flash can be reprogrammed using one of these techniques:

- Select the 21285's *blank ROM programming mode* via a jumper on the EBSA-285 and plug the board into an Intel PC, then reprogram block 0 across the PCI bus.

- Program the flash ROM via the 21285 JTAG port.

The EBSA-285 is supplied with a software utility that allows images to be programmed into flash ROM either across the PCI bus, as described above, or under the control of the ARM toolkit's remote debugger. This utility, the Flash Management Utility (FMU), is described in Chapter 7.

Software for reprogramming flash ROM via the 21285 JTAG port may be provided in future releases of the EBSA-285 software.

#### 2.3.3 EPROM Emulator

An EPROM emulator is a debugging tool that connects to a target as though it were an EPROM but allows fast download and modification of code.

The EBSA-285 has a 32-pin 0.6-inch DIL socket that can be used to connect a byte-wide 512-KB EPROM emulator head.

A conventional EPROM **cannot** be fitted to this socket. This is because the socket provides 3.3-V power, and a WE line (not found on EPROMs). Similarly, only 3.3-V EPROM emulators can be used.

Warning: Fitting a 5-V emulator may result in damage to your EBSA-285.

Jumpers on the EBSA-285 are used to reconfigure the ROM width and disable the flash ROM in this mode; access to the flash ROM and the EPROM emulator socket are mutually exclusive.

When the EBSA-285 is configured correctly, the 21285 makes SA-110 and PCI accesses to the EPROM emulator appear as 32-bit accesses.

The PROMJet<sup>™</sup> EPROM emulator, from EmuTec, has been used successfully on the EBSA-285. Details from:

Telephone number in the United States of America: +1 425 267 9604

The company web page: http://www.emutec.com

#### 2.3.4 Memory-Map Switching

Immediately after reset, the 21285 decodes the flash ROM at two locations; at its normal base address in high memory and also at an alias of 0. Decoding at this alias allows the SA-110 to fetch its reset vector. The alias is disabled by the first store (write) instruction executed by the SA-110.

### 2.4 I/O Subsystem

All local I/O (within the EBSA-285 module) is performed as programmed I/O under the control of the SA-110. The I/O subsystem provides the following resources:

- An RS-232 console port (data leads only) accessed via a 9-way D-type on the bulkhead. This is referred to as COM0.

- An 8-bit I/O port used to control LEDs and read the state of jumpers and a switch.

The only other I/O facilities on the board are those provided by the 21285 itself.

### 2.5 Interrupts

When the EBSA-285 is used as a Host Bridge (21285 configured as Central Function), logic in the 21285 acts as an interrupt controller for interrupts generated locally (on the module and within the 21285) and for interrupts generated by other devices on the PCI.

When the EBSA-285 is used as an add-in card, logic in the 21285 acts as an interrupt controller for interrupts generated locally (on the module and within the 21285). In this mode, the SA-110 can generate an interrupt to the Host Bridge (across the PCI bus) under software control. The interrupt is routed out of the EBSA-285 as INTA#.

## 2.6 PCI Interface

The EBSA-285 has a 32-bit PCI interface that is compliant with Revision 2.1 of the PCI Local Bus specification. It supports both 3.3-V and 5-V signalling.

The EBSA-285 has the capability either to generate or to respond to configuration cycles on the PCI bus. These cycles are normally performed by a Host Bridge, however, they can be generated by an add-in card, for example, to determine the PCI access to system memory.

# 2.7 PCI Bus Arbiter

The 21285 contains a PCI bus arbiter. When the EBSA-285 is configured as a Host Bridge, and plugged into a suitable backplane, the EBSA-285 can provide arbitration for the 21285 itself plus up to four devices on the PCI.

The PCI Bus Arbiter cannot be used at the same time as the X-Bus (since they share signal pins on the 21285). A set of jumpers on the EBSA-285 enables one or the other.

**Note:** When the PCI Bus Arbiter is enabled the X-Bus is disabled, so the EBSA-285 LEDs and flash image selector switch cannot be used.

## 2.8 **JTAG**

The SA-110 and the 21285 both contain JTAG ports that allow test access to the I/O pins of the device.

The EBSA-285 daisy-chains the two JTAG ports and provides access to the port through a 7x2 0.1-inch pitch header connector.

It is recommended that all ROM communications performed by the programming software tool, be done through the DS21285 JTAG Boundary Scan chain. The micro-processor should be held in the reset state by asserting nRESET signal low, so as to grant access to address and data buses.

The Test Access Port (TAP) is buffered from the connecting source device by a standard 74ACT244 device. The physical connection to the TAP is made to the board by a 14 way IDC connector. Table 2–1 shows the IDC connector pinout.

| Pin | Туре           | Use         | Polarity   |

|-----|----------------|-------------|------------|

| 1   | _              | 33R to +5 V | _          |

| 2   | _              | GND         | _          |

| 3   | Input to board | TRST_L      | Active low |

| 4   | _              | NC          | _          |

| 5   | Input to board | TDI         | Normal     |

| 6   | _              | GND         | _          |

| 7   | Input to board | TMS         | Normal     |

Table 2–1 TAP IDC Connector Pinout

#### JTAG

| Pin | Туре              | Use                  | Polarity   |

|-----|-------------------|----------------------|------------|

| 8   | _                 | GND                  | _          |

| 9   | Input to board    | TCK                  | Normal     |

| 10  | _                 | GND                  | _          |

| 11  | Output from board | TDO                  | Normal     |

| 12  | Input to board    | SRST_L – Board reset | Active low |

| 13  | _                 | Connected to pin1    | _          |

| 14  | -                 | GND                  | _          |

Table 2–1 TAP IDC Connector Pinout

This pinout is compatible with ARM PCBs and microprocessors.

Table 2–2 shows the signals on Test Access Ports (TAPs).

Table 2–2 Signals on the TAP

| Signal Name             | Pull-up | Sampled/Updated on<br>Clock Transitions From-to | Optional |

|-------------------------|---------|-------------------------------------------------|----------|

| Test Data In (TDI)      | Yes     | Low to high                                     | No       |

| Test Data Out (TDO)     | No      | High to low                                     | No       |

| Test Clock input (TCK)  | No      | _                                               | No       |

| Test Mode Signal (TMS)  | Yes     | Low to high                                     | No       |

| Test Reset input (TRST) | Yes     | Asynchronous                                    | Yes      |

The JTAG registers available are shown in Table 2–3.

| Register             | Purpose                                                             |  |  |  |

|----------------------|---------------------------------------------------------------------|--|--|--|

| Instruction register | Holds the current instruction op-code value for the following task. |  |  |  |

| Boundary scan        | Reads and writes data to physical device connection pins.           |  |  |  |

#### Table 2–3 JTAG Registers

### JTAG

| Register                              | Purpose                                                                            |

|---------------------------------------|------------------------------------------------------------------------------------|

| Bypass                                | Shortcuts the route of the JTAG daisy chain. Register is one cell long per device. |

| Device ID                             | Read out a preprogrammed compounded device information number.                     |

| Design specific test<br>data register | Test data register used by IC manufacturers                                        |

#### Table 2–3 JTAG Registers

The JTAG commands available are shown in Table 2–4.

| Command  | Nature | Op-Code      | 285 Value |

|----------|--------|--------------|-----------|

| EXTEST   | Public | All 0's      | 0000      |

| SAMPLE   | Public | User defined | 0001      |

| BYPASS   | Public | All 1's      | 1111      |

| INTEST   | Public | User defined |           |

| RUNBIST  | Public | User defined |           |

| IDCODE   | Public | User defined | 0100      |

| USERCODE | Public | User defined |           |

| CLAMP    | Public | User defined | 0011      |

| HIGHZ    | Public | User defined | 0010      |

Table 2–4 JTAG Commands

# 2.9 Expansion

The I/O capabilities of the EBSA-285 can be expanded in two ways:

- The PCI interface.

- The expansion headers of the buffered 21285 X-Bus. These allow a small mezzanine PCB to be attached for connection to the X-Bus. The X-Bus provides a simple way of providing access to low-performance I/O.

# 2.10 Clocks

The EBSA-285 uses these oscillators:

- 3.6864 MHz oscillator: This oscillator is used for two purposes. Firstly, it is used to drive the SA-110 phase-locked loop (PLL) input, from which the SA-110 generates its core clock. Secondly, it is used to provide a fixed frequency input to one of the timers in the 21285.

- 50 MHz oscillator: This oscillator provides the osc input clock for the 21285. The 21285 buffers and redrives this clock to generate the SA-110 bus clock, the SDRAM clocks and the 21285 feedback clock, fclk. The local buses and the majority of the 21285's internal logic run synchronously at this clock frequency.

- When the EBSA-285 is plugged into a backplane (either as an add-in card or a Host Bridge) it receives PCI clock from the backplane.

# 2.11 Resets

There are three sources of reset on the EBSA-285:

- Power-on reset

- Reset from PCI

- Reset from the 21285 watchdog timer

Power-on reset is generated automatically when power is applied to the EBSA-285. It can also be initiated by:

- A push-button switch attached to a 2-pole 0.1-inch pitch connector on the board

- Circuitry connected to the JTAG test connector

Resets generated by any of these methods are equivalent and indistinguishable.

#### **Power Requirements**

When the EBSA-285 is run in Central Function mode, the circuitry on the board is reset by power-on reset and the 21285 generates PCI reset output under software control.

In Central Function mode, the 21285 watchdog timer can be used to reset the whole system in a way that is equivalent to a power-on reset.

When the EBSA-285 is run in non-Central Function mode, it receives reset from the PCI and this reset is used to reset all of the circuitry on the board.

### 2.12 Power Requirements

The EBSA-285 has the following power requirements:

- + 5-V +/-5%, @ 1.0 A

- + 12-V +/-5%, @ 250 mA

When the EBSA-285 is plugged into a backplane (either as a Host Bridge or an addin card), it draws power from the PCI edge connector.

The EBSA-285 will function without the + 12-V supply; that supply rail is only used to allow reprogramming of the flash ROMs.

# 2.13 Onboard Power Generation

The EBSA-285 generates + 3.3-V and + 2-V using onboard circuitry.

The +3.3V is generated from +5-V using a dc-dc converter. The +3.3-V is used to supply the flash, the SDRAMs, the 21285 and various data and address buffers.

The +2V is generated from +3.3-V using a linear regulator. The +2 V is used to supply the core voltage for the SA-110.

**Note:** Although the EBSA-285 supports both + 3.3-V and + 5-V signalling on the PCI bus, it never draws + 3.3-V power from a PCI connector; it always requires + 5-V.

# 2.14 Onboard Software

The EBSA-285 onboard software is programmed into the flash ROM. The flash ROM can contain a number of independent images. At a minimum, the flash ROM contains a program called the Primary Boot Loader (PBL). The PBL can load and

start a specific image that is stored in flash ROM and selected using the rotary flash image selector switch on the bulkhead mounting bracket. By default, the PBL starts up the ARM remote debug agent.

An onboard diagnostic suite is also programmed into flash ROM and can also be selected by means of the rotary switch.

# **3** Programmer's Guide

Much of the functionality on the EBSA-285 is fixed by the design of the 21285. This chapter describes the facilities that are specific to the EBSA-285. These are:

- The flash memory

- The SDRAM memory

- The X-Bus memory-map

- Interrupt assignment

- Timer assignment

- The soft input/output port

- The reset state of the system

This chapter, in conjunction with the 21285 Data Sheet, should act as a complete reference for programmers of the EBSA-285.

## 3.1 Flash Memory

Non-volatile code storage is provided by four 1-MB flash ROMs. These are Intel 28F008 parts. They are arranged to provide a 32-bit boot path for the SA-110.

Each flash ROM provides sixteen 64-KB blocks of memory. The blocks are contiguous but can be erased and programmed separately. Because the flash is arranged as 32-bit memory, it can be treated as sixteen 256-KB blocks decoded at addresses 0x4100.0000 - 0x413F.FFFF.

A new EBSA-285 contains debugger and self-test images in the first two blocks of the flash ROM. User code can be programmed into other blocks. A utility for managing images in flash ROM is described in Chapter 7.

The EBSA-285 can be configured to accommodate an 8-bit ROM emulator, which attaches via a 32-pin 0.6-inch DIL socket on the board. Refer to Section 2.3.3 for information on choosing and using a ROM emulator.

## 3.2 SDRAM Memory

The EBSA-285 can accommodate two 168-pin 3.3-V SDRAM DIMMs. The standard configuration is to fit a single 16-MB DIMM, which appears as two 8-MB arrays decoded at addresses 0x0 - 0xFF.FFFF. Section A.5 describes how to upgrade or change the configuration of the DIMM. Section 4.7 describes how to initialize the 21285's memory controller to enable access to the SDRAM.

## 3.3 X-Bus Memory-Map

The X-Bus is used for accesses to external low-speed I/O devices. There are four separate address spaces. On the EBSA-285 the only address space that is used is the XCS2 address space, 0x4001.2000 - 0x4001.2FFF. All accesses in this region alias to the soft input/output register, which is described in Section 3.6. The remaining X-Bus address regions could be used by a mezzanine daughtercard attached to the EBSA-285.

Initialization of the X-Bus is described in Section 4.4.

## 3.4 Interrupt Assignment

The 21285 allows some of its external pins to be used as interrupt inputs. The assignment of these signals on the EBSA-285 is shown in Table 3–1.

| Signal    | Bit in IRQ<br>Status | Assignment                                                                                                                 |

|-----------|----------------------|----------------------------------------------------------------------------------------------------------------------------|

| pci_irq_l | 18                   | When the EBSA-285 is configured as the Host Bridge and plugged into a PCI backplane, this bit supplies INTA# from the PCI. |

| xcs_l[2]  | 14                   | This bit would never normally be enabled as an interrupt on the EBSA-285.                                                  |

| xcs_l[1]  | 13                   | This bit is unassigned on the EBSA-285. It could be used on an X-Bus daughtercard.                                         |

| xcs_l[0]  | 12                   | This bit is unassigned on the EBSA-285. It could be used on an X-Bus daughtercard.                                         |

Table 3–1 Interrupt Assignment

|             | Bit in IRQ |                                                                                                                                                                                           |

|-------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal      | Status     | Assignment                                                                                                                                                                                |

| irq_in_l[3] | 11         | When the EBSA-285 is configured as the Host Bridge and plugged into a PCI backplane, this bit supplies INTD# from the PCI.                                                                |

| irq_in_l[2] | 10         | This input is driven from a fixed 3.68-MHz oscillator. It is nor-<br>mally used to increment Timer 3, as described in Section 3.5. It<br>would never normally be enabled as an interrupt. |

| irq_in_l[1] | 9          | When the EBSA-285 is configured as the Host Bridge and plugged into a PCI backplane, this bit supplies INTC# from the PCI.                                                                |

| irq_in_l[0] | 8          | When the EBSA-285 is configured as the Host Bridge and plugged into a PCI backplane, this bit supplies INTB# from the PCI.                                                                |

Table 3–1 Interrupt Assignment

Each of these interrupts has programmable polarity.

### 3.5 Timer Assignment

The 21285 has four internal timers. These can be incremented by clocks internal to the 21285 or by an external input.

If timer 3 is configured to increment from an external input, it will be clocked from the SA-110 PLL input oscillator, and will count at a rate of 3.68 MHz. This is the only independent fixed oscillator frequency on the board and it can be used to infer the system bus speed, the PCI clock speed, and the SA-110 core clock speed.

## 3.6 Soft Input/Output Register

The bulkhead mounting bracket of the EBSA-285 holds three LED indicators (one each red, amber and green) and a 16-position switch. The soft input/output port allows software to control the state of the LEDs and read the state of the switch. Software can also read the state of three onboard jumpers. The bit assignment of this register is shown in Table 3–2.

#### Soft Input/Output Register

| Bit | Name     | Туре       | Description                                                                                                                                                                                                                                                                                     |

|-----|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TOGGLE   | Read/Write | This bit acts as a read/write bit and has no other<br>effect. Its intention is to provide a bit that can be tog-<br>gled under software control to provide some indica-<br>tion that the X-Bus can be accessed successfully.                                                                    |

| 6:3 | Unused   | Write-only | These bits are unused on writes; data is don't-care.                                                                                                                                                                                                                                            |

| 2   | RED_L    | Write-only | Write a 0 to illuminate the red LED, write a 1 to extinguish the red LED.                                                                                                                                                                                                                       |

| 1   | GREEN_L  | Write-only | Write a 0 to illuminate the green LED, write a 1 to extinguish the green LED.                                                                                                                                                                                                                   |

| 0   | AMBER_L  | Write-only | Write a 0 to illuminate the amber LED, write a 1 to extinguish the amber LED.                                                                                                                                                                                                                   |

| 6   | IBUF6    | Read-only  | Read the state of jumper J17 pins 9-10. Read '1' if<br>the jumper is removed, '0' if the jumper is fitted. This<br>bit is used by the supplied initialization software to<br>determine whether or not the EBSA-285 should per-<br>mit access to PCI. PCI accesses are enabled when fit-<br>ted. |

| 5   | IBUF5    | Read-only  | Read the state of jumper J17 pins 11-12. Read '1' if the jumper is removed, '0' if the jumper is fitted.                                                                                                                                                                                        |

| 4   | IBUF4    | Read-only  | Read the state of jumper J17 pins 13-14. Read '1' if the jumper is removed, '0' if the jumper is fitted.                                                                                                                                                                                        |

| 3:0 | SWITCH_L | Read-only  | Read the state of the 16-position switch. The data is<br>the inverse of the value selected on the switch, so that<br>this nibble will read 0xf when the switch is set to '0',<br>0xe when the switch is set to '1', and so forth.                                                               |

Table 3–2 Bit Assignment of Soft Input/Output Register

Onboard software adopts a consistent policy for the use of the LEDs, the rotary switch and the jumpers. This is described in Chapter 6.

## 3.7 The Reset State of the System

After reset, the 21285 SDRAM controller and the X-Bus are disabled. The 21285 decodes the flash ROM at two locations; at its normal base address and also at an alias of 0.

Since the 21285 SDRAM controller is disabled by reset, SDRAM contents is UNDEFINED after reset.

## 4

## **Software Configuration and Initialization**

Software must initialize the system hardware after a power up or reset. This chapter provides guidelines for the various initialization steps that need to be taken.

The software that is loaded into the system by the Primary Boot Loader or by a remote debug agent such as Angel can make assumptions about what in the system has already been configured. The state of the run-time environment in these different situations is described in Chapter 6.

The correct sequence for the initialization steps required after reset is:

- 1. Disable the flash ROM alias at address 0.

- 2. Determine the board configuration.

- 3. Initialize the X-Bus or PCI bus arbiter.

- 4. Initialize the SDRAM.

- 5. Configure the 21285 UART (optional).

- 6. Configure the PCI interface (optional).

- 7. Configure the SA-110 memory-management unit (MMU), turning on virtual memory, clock switching and caches (optional).

## 4.1 Disabling the Flash ROM Alias

After reset, the 21285 decodes the flash ROM at two locations; at its normal base address of 0x4100.0000 and also at an alias of 0. Decoding at this alias allows the SA-110 to start executing from the normal reset vector address of 0. Once the first write operation has been executed by the SA-110, the alias is disabled.

Software should branch to the high-order alias of the flash ROM before executing the first write operation.

## 4.2 Accessing the Flash ROM

After reset and in normal operation, the flash ROM appears as a 32-bit read-only device. It is actually implemented using four, 8-bit devices that are accessed in parallel. Flash operations other than simple ROM operations are selected by writing specific commands into the Command User Interface. Refer to the Intel 28F008SA data sheet for details of the commands.

The four flash parts can be accessed individually or simultaneously, depending upon whether commands are sent to all parts simultaneously or to a subset of the parts. For example, programming a flash location is achieved by writing 0x40 to a byte location followed by writing a data byte to the same location. A write of 0x40404040 to any EBSA-285 flash location followed by a write of 0xabcd.ef01 to the same location will result in 0xabcd.ef01 being programmed into the location (one byte programmed into each of the four flash devices). However, a write of 0x40000040 to an EBSA-285 flash location followed by a write of 0xabcd.ef01 to the same location will result in the 0xab and 0x01 bytes being programmed and the other two bytes of the longword being unchanged.

#### 4.2.1 Programming the Flash from the SA-110

The SA-110 must not be executing from flash ROM when it executes a flash programming algorithm. The reason for this is that flash programming requires a defined sequence of reads and writes to the flash. Code fetches would disrupt the sequence.

The Angel debug monitor relocates itself into SDRAM after power-up. The standard flash management utility also executes from RAM, thus avoiding any code fetches when programming flash.

#### 4.2.2 Programming the Flash from the PCI Interface

Before programming the flash from the PCI interface, the 21285 *ROM Write Byte Address Register* must be set to 0.

The 21285 allows the flash to be reprogrammed from the PCI interface while the SA-110 is running (though this will only work correctly if the SA-110 is not accessing the flash). However, the 21285 also provides a special mechanism for reprogramming flash, called 'Blank ROM Mode'. On the EBSA-285, this mode is selected by moving a jumper on J15 (refer to Section A.2.2.3 for details).

## 4.3 Determining the Card Configuration

The EBSA-285 can be used in various modes, all selected by jumper, and it may be necessary for software running on the board to behave differently in the different modes. Two bits identify the configuration of the board:

- Bit 23 of the 21285 *X-Bus Cycle/Arbiter Register* the X-Bus/Arbiter bit: The 21285 is configured, at power up, to enable *either* its X-Bus *or* its internal PCI bus arbiter. Depending upon which mode is selected, software should initialize the appropriate registers, as described in Section 4.4 and Section 4.5. If the X-Bus is disabled, the soft input/output register described in Section 3.6 cannot be used.

- Bit 31 of the 21285 *SA-110 Control Register* the CFN bit: The 21285 is configured, at power up, to act either as a Host Bridge (CFN asserted) or an add-in card.

## 4.4 Initializing the X-Bus

If the X-Bus is enabled, it should be configured by writing to the 21285 X-Bus Cycle/ Arbiter Register and X-Bus I/O Strobe Mask Register. The X-Bus I/O Strobe Mask Register is also used to set the polarity of some of the 21285 interrupt inputs. A suitable initialization sequence for the EBSA-285 is:

- 1. Write 0x1000.16db to the 21285 X-Bus Cycle/Arbiter Register.

- 2. Write 0xfcfc.fcfc to the 21285 X-Bus I/O Strobe Mask Register.

- 3. Write 0x6000.0000 to the 21285 *SA-110 Control Register* (to enable X-Bus chip selects 2 and 1).

## 4.5 Initializing the PCI Bus Arbiter

If the PCI bus arbiter is enabled, it may be configured by writing to the 21285 *X-Bus Cycle/Arbiter Register*. The arbiter will work correctly with the default (power up) values in this register.

## 4.6 Setting the INITIALIZE\_COMPLETE Bit

If the EBSA-285 is configured as an add-in card, plugged into a PC, the PC will attempt to access the EBSA-285's PCI configuration registers as part of the PC's power up self-test (POST) sequence. After reset, the 21285 will cause a PCI retry in response to a PCI configuration cycle. Unless software on the EBSA-285 configures

the PCI interface, this will cause the PC to retry forever, so that it appears to 'hang'. The minimum initialization required to avoid this is to set bit 0 (INITIALIZE\_COMPLETE) in the 21285 SA-110 Control Register. A more sophisticated initialization is described in Section 4.9.

## 4.7 Initializing the SDRAM

Two sets of operations are required in order to allow access to the SDRAM:

- Configure the 21285 memory controller registers.

- Configure the mode registers in the SDRAM arrays.

This section provides a sample configuration, coded in ARM assembler. The code assumes that all four SDRAM arrays are populated with 2Mx8 parts that can run with a latency of 2.

1. Start with a set of equates for registers and register values.

| CSR_BASE          | EQU | &42000000 |  |  |

|-------------------|-----|-----------|--|--|

| SDRAM_TIMING      | EQU | &10C      |  |  |

| SDRAM_ADDR_SIZE_0 | EQU | &110      |  |  |

| SDRAM_ADDR_SIZE_1 | EQU | &114      |  |  |

| SDRAM_ADDR_SIZE_2 | EQU | &118      |  |  |

| SDRAM_ADDR_SIZE_3 | EQU | &11C      |  |  |

| CMD_DRIVE         | EQU | &800      |  |  |

| PARITY_ENABLE     | EQU | &1000     |  |  |

| Tref_min          | EQU | &010000   |  |  |

| Tref_norm         | EQU | &1A0000   |  |  |

| Trp               | EQU | &1        |  |  |

| Tdal              | EQU | &4        |  |  |

| Trcd              | EQU | &20       |  |  |

| Tcas              | EQU | &80       |  |  |

| Trc               | EQU | &300      |  |  |

2. After reset, the SDRAM arrays are in an unknown state. To put them into a known state, force an all-banks precharge to each of the four possible arrays. You must access all four arrays for this even if all four are not fitted. This is necessary because the 21285 counts these precharge accesses, and inhibits access to the SDRAM until all four have been completed. Failure to perform four precharge accesses will result in unpredictable operation. An all-banks precharge is initiated by a read from any address in the mode register address space.

```

r0,=&40000008 ; SDRAM array 0

ldr

ldr

r0,[r0]

r0,=&40004008 ; array 1

ldr

ldr

r0,[r0]

r0,=&40008008 ; array 2

ldr

ldr

r0,[r0]

ldr

r0,=&4000C008 ; array 3

ldr

r0,[r0]

```

3. Write to the *SDRAM Mode Register* in the SDRAMs. This requires one write operation for each SDRAM array. The address is important, not the data. The offset from the start of the mode space for each SDRAM array controls what data is written to the SDRAM mode register. The mode register should be configured for a burst size of 4 and for linear addressing.

| ldr | r0,=&40000008:OR:Tcas |

|-----|-----------------------|

| str | r0,[r0]               |

| ldr | r0,=&40004008:OR:Tcas |

| str | r0,[r0]               |

| ldr | r0,=&40008008:OR:Tcas |

| str | r0,[r0]               |

| ldr | r0,=&4000C008:OR:Tcas |

| str | r0,[r0]               |

4. Write to the *SDRAM Timing Register* in the 21285. Set the refresh interval to the minimum because we have to wait for 8 refresh cycles to complete before we can rely on the SDRAMs operating normally.

5. Wait for 8 refresh cycles to complete. The minimum refresh interval is 32 cycles and we are currently running with the Icache off, so the complete process will take 256 cycles.

|      | ldr  | r0,=&100 |

|------|------|----------|

| wait | subs | r0,r0,#1 |

|      | bgt  | wait     |

6. Write to the four 21285 *SDRAM Address and Size Registers*. This simple code assumes four arrays are fitted and that they are all the same size and type. More sophisticated code would automatically detect and size each array.

```

ldr

r0,=&14

str

r0,[r1,#SDRAM ADDR SIZE 0]

ldr

r0,=&800014

str

r0,[r1,#SDRAM_ADDR_SIZE_1]

r0,=&1000014

ldr

r0,[r1,#SDRAM_ADDR_SIZE_2]

str

ldr

r0,=&1c00014

str

r0,[r1,#SDRAM_ADDR_SIZE_3]

```

7. Finally, reset the refresh interval to a sensible value. Continuing to run with a very short interval would waste memory bandwidth. The refresh interval is calculated to refresh 4096 rows in 64ms.

## 4.8 Re-initializing the SDRAM

The 21285 only allows SDRAM mode writes to be performed when refresh is disabled. Therefore, the initialization sequence shown in the previous section cannot be re-executed. Either of the following two modifications will allow the code to be reexecuted:

- At the start of the sequence, read the 21285 *SDRAM Timing Register* and check whether refresh is enabled (refresh interval set to a non-zero value). If it is enabled, you can infer that the SDRAM initialization has already been performed and that no further action is needed. If refresh is not enabled, you can execute the initialization sequence described in Section 4.7.

- At the start of the sequence, disable refresh by setting the refresh interval to 0, then wait for 15 bus clock cycles to ensure that any pending or in-progress refresh completes successfully. You can then execute the initialization sequence described in Section 4.7.

## 4.9 Initializing the PCI Interface

This section describes the minimum set of PCI registers that must be configured to allow the PCI interface to be used.

- 1. Start by setting some important registers to a known state as follows:

- Write 0xc in the 21285 *Outbound Interrupt Mask Register* (disable outbound interrupts).

- Write 0x0 in the 21285 *Doorbell PCI Mask Register* (clear doorbell interrupts to PCI).

- Write 0x0 in the 21285 *Doorbell SA-110 Mask Register* (clear doorbell interrupts to the SA-110).

- Write 0x0 in the 21285 *PCI Address Extension Register* (set it to a known state).

- Write 0x1 in the 21285 *Interrupt Line Register* (some PCI systems do not correctly recognise an interrupt ID of 0).

- 2. Negate the PCI reset signal (this only has an effect if the EBSA-285 is the Host Bridge it is ignored otherwise):

- Set bit 9 (PCI not reset) in the 21285 SA-110 Control Register.

- 3. Open up a window from PCI memory space into the EBSA-285 SDRAM address space. If the EBSA-285 is configured as an add-in card, configuring this window will allow the host PC to allocate PCI memory address space for the EBSA-285 when it performs its POST. To create an 8-MB window:

- Write 0x007c.0000 to the 21285 SDRAM Base Address Mask Register.

- 4. The next step must only be performed if the CFN bit is set and the bench test bit is clear (refer to Section 4.3):

- Write 0x0 to the 21285 *Command Register*. This stops the 21285 from responding to any PCI transactions.

- Write 0x4000.0000 to the 21285 CSR Memory Base Address Register.

- Write 0xf000 to the 21285 CSR I/O Base Address Register.

- Write 0x0 to the 21285 SDRAM Base Address Register.

- Write 0x17 to the 21285 *Command Register*. This enables the 21285 as a bus master and allows it to respond to I/O space and memory space transactions as target.

5. Finally, set bit 0 (INITIALIZE\_COMPLETE) in the 21285 *SA-110 Control Register*. This will allow the EBSA-285 to respond to PCI configuration cycles, as described in Section 4.6.

## 4.10 Initializing the 21285 UART

The EBSA-285 runs with an **fclk\_in** frequency of 50 MHz. The frequency of **fclk\_in** determines what divisors are appropriate when configuring the 21285's internal UART. Table 4–1 shows baud rate divisors for this bus frequency.

| Baud Rate | Divisor | Error  |

|-----------|---------|--------|

| 50        | 15624   | 0.00%  |

| 75        | 10416   | 0.00%  |

| 110       | 7101    | 0.00%  |

| 134.5     | 5808    | 0.01%  |

| 150       | 5207    | -0.01% |

| 300       | 2603    | -0.01% |

| 600       | 1301    | -0.01% |

| 1200      | 650     | -0.01% |

| 1800      | 433     | -0.01% |

| 2000      | 390     | 0.10%  |

| 2400      | 325     | 0.15%  |

| 3600      | 216     | -0.01% |

| 4800      | 162     | 0.15%  |

| 7200      | 108     | 0.45%  |

| 9600      | 80      | -0.47% |

| 19200     | 40      | 0.76%  |

| 38400     | 19      | -1,73% |

| 56000     | 13      | 0.35%  |

| 128000    | 5       | -1.73% |

Table 4–1 21285 Baud Rate Divisors for 50 MHz fclk\_in

## 4.11 Configuring Cacheable/Non-Cacheable Space